开篇先打个广告:

你的点赞加关注将是激励我持续输的出动力!

广义上讲,由互连线引起的所有的问题。

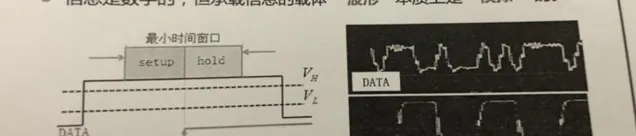

包括:时序、噪声、电磁干扰;简单的理解,就是在一个周期如何分配合理时隙,使得IC能转换成合理的数据。

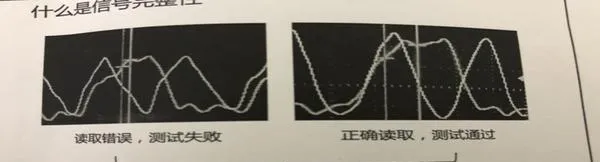

噪声是主要要解决的问题,它包含振铃、反射、串扰、开关噪声、非单调性、电源噪声。

所有与信号完整性噪声问题有关的问题可以总结为4类:

所有与信号完整性噪声问题有关的问题可以总结为4类:

- 单一网络的信号完整性

这里面有一个很重要的概念,作为硬件工程师,一定要形成条件反射:

返回路径

单一网络的信号质量与返回路径物理特征有很大关系。如果记住这个点,很多layout的错误很容易被发现。

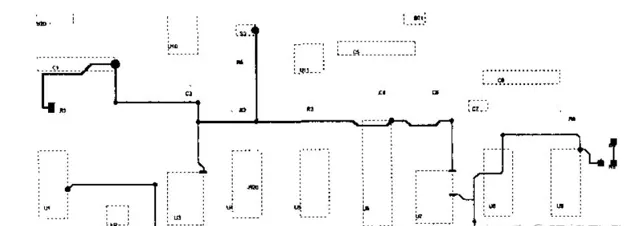

关键信号要注意的点:

线宽是否变化(这个要更加特征阻抗确定)

参考平面是否完整

是否有分支线

特征阻抗是否连续

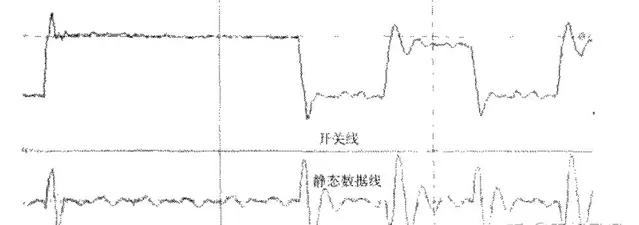

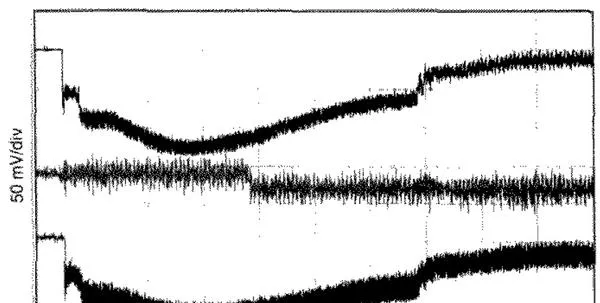

2. 两个或多个网络的串扰

这主要解决的是线与线之间的耦合关系,我们通常说3W间距,地孔隔离带,减少平行走线的长度等就是为了解决线与线之间的干扰。

这个地方可以从特征阻抗模型分析,平行线有电感耦合与电容的因素。这样在信号传输的过程中总有充放电和电磁耦合的现象。

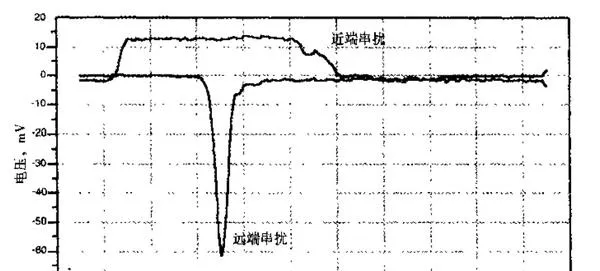

串扰可以分为近端耦合,与远端耦合,近端耦合很容易饱和,远端耦合幅值很大。

后面章节会具体说明。

3. 电源和地的轨道塌陷

这个就是电源压降。

本质上是由互连线之间的阻抗过大造成的。当电流过大,而目标阻抗过大所造成的电压跌落现象。

也就是我们经常会看到,目标阻抗最小化问题。

在原理图设计的时候:耦合电容的容值选择,数量的选择;

在PCB设计的时候:电容去耦半径,过孔寄生电容和电感,电源层的设置,封装寄生效应;

电源完整性我也会在后续章节来介绍。

4. 系统电磁干扰和辐射

分为EMI和EMC

目前,国内开始重视EMC的管控,我的每个产品都有EMC要求,最近几年基本上是解决EMC问题。因为这东西和原理关系不大,主要是参数选择和布局走线的控制。

我们通常会听到整改方案提到一对关键词: 共模和差模 ;

共模辐射强度和频率是线性关系。

差模辐射强度和频率是平方关系。

辐射问题,我们要有意识的定位三个问题:

噪声源 :这个过程就比较复杂了,需要你熟悉系统的信号流向。

辐射路径 :有线和无线

天线 :接口连线,插接

注:减小回路面积和伴地处理在很多情况下是非常有效的手段。

总结随着项目经验丰富,你会发现信号完整信本质上就是在解决阻抗问题。

阻抗会引起信号失真,会导致电源压降,会导致辐射。

业界一直有两种人:经验主义和理论主义.

前者过分套用所谓的准则,让设计很被动,总是畏手畏脚。

后者过分最求参数,虽然可靠性上来了,但是设计成本和周期也成倍增长。

我认为,结果是最好的经验,一切都要在成本和时间面前妥协。

有限的精力放在相对关键的信号上。

其他信号,多一点少一点,关系真不大。

后面文章中,我会从多个角度重点分析。

关注王叔日记

你的点赞加关注将是激励我持续输出动力!