幾個高贊回答都提到了物理制程和標稱制程是不一樣的。物理制程有天花板,而廠商所說的3nm、2nm更像是一種命名遊戲或宣傳噱頭,這些數位都不再代表實際導電溝道的尺寸,並且由於標準不一樣,這些數位所衡量的位置沒有統一的標準,同樣是 7nm,物理大小也許完全不一樣, 5 nm也可能比 7 nm更大,很難說誰比誰更先進。

但為什麽人們不再用真實的工藝命名?為什麽衡量工藝的「標準」一下混亂起來?在這背後,人類實際上經歷了一次「技術路線的終結」和一次涅槃性的突破。

我們曾經做過一個視訊解釋了這一歷程,

芯片卷奈米數,真進步還是假話術

https://www.zhihu.com/video/1706627432168353792

芯片卷奈米數,真進步還是假話術

https://www.zhihu.com/video/1706627432168353792

視訊對於差點終結人類算力進步的「漏電」問題,以及胡正明的解決方案介紹的比較簡單,下面我們展開說說。(也歡迎移步騰訊視訊或b站搜尋觀看完整視訊)

一切從芯片的構造和原理說起。

拆開一枚芯片,構成芯片最基本的單元是晶體管。它是一個開關,能在導電和絕緣兩種狀態之間反復橫跳,對應著電腦中的訊號 1 和訊號 0。決定是「開」還是「關」的是這裏的電壓。

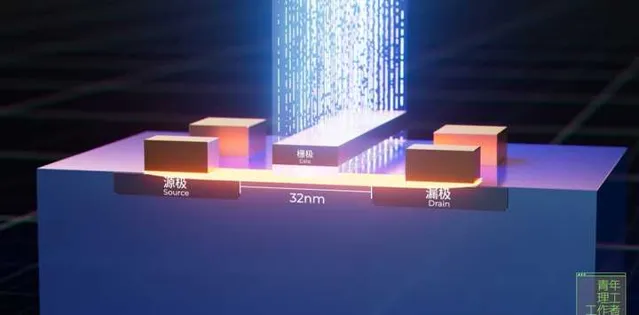

電壓是被載入在中間這塊導電的金屬上的,它叫做柵極。一會導電一會絕緣的地方是下方的半導體,其實就是矽本身。矽裏面被摻入了其他原子,根據摻雜的原子種類的不同,半導體的部份又被分為源級、漏級、襯底。

由於摻入了不同的原子,源極、漏極的內部都是導電的,而它們之間的部份並不導電。

隨著電壓一點點被施加,中間絕緣部份的表面會漸漸形成一個可以導電的區域,將源和漏導通在一起。它叫導電溝道,雖然名字叫溝道,但它其實是半導體表面一個非常非常薄的可以導電的薄層。 通常,人們用導電溝道的長度代表晶體管的工藝,或者說晶體管有多小,比如 32 奈米工藝說的就是這裏。

而這種平面型晶體管(也叫MOS管)的特殊效能決定了,它的溝道越短,效能越好。這是非常神奇的特性,因為對於大部份晶體管而言,變小的最大限制是發熱,如果上億份熱量集中到1 平方厘米的面積,工作時散發的熱量本身就可以把芯片燒毀。只有 MOS 管能在 1 平方厘米的空間內堆滿上百萬甚至上億個,因為當一個 MOS 管變小時,一切都會變得更好:功耗下降,與功耗相伴的發熱也隨之降低,甚至每一個管的速度也會變得更快。

但是,當溝道長度縮短到一定程度時,會發生一個現象——漏電!

漏電是什麽?還是拿平面型 MOS 管舉例,源極接地,也就是 0V;漏極接正的電源電壓,假如說是 5V;絕緣體外的柵極接輸入訊號,也就是在 0V 和 5V 之間來回跳轉,它們分別代表訊號 0,訊號 1。這便是 MOS 管日常的工作狀態。

當尺寸小的一定程度時,半導體會誤把漏極的電壓當成柵極的電壓,形成持續的漏電流。這會讓晶體管一直處於半導通的狀態,持續耗電,讓整體的功耗增加,也無法清晰區分訊號0和1。

最初解決漏電的辦法是讓有用的電壓訊號重獲控制權,也就是讓中間的絕緣體變薄,讓柵極電壓距離半導體近一些。更薄的絕緣體讓柵極的訊號距離更近,對抗漏極電壓幹擾的能力越強。

當絕緣體厚度接近一層原子的厚度時,就不能變得更薄了,也就是零點幾奈米。此時對應的溝道長度是 35 奈米,也就是這種晶體管的終結。 也就是說,35nm芯片就是這一制程的極限。 無法解決漏電,芯片就不可能再小了!20世紀80年代,大家就已經發現了這一局限,此後各種方案陸續登場,但或是技術或是成本的原因,這些方案又被一次次拋棄。大家預測,2010 年工藝將來到 35 nm,也就是算力的末日。

但我們現在都在討論3nm的芯片是不是芯片制程的天花板了,這中間發生了啥?

這就不得不說到一個華人科學家胡正明,是他打破了這一魔咒。

1999年,他發現,半導體越薄,漏電流越小,只要夠薄,就能解決漏電。

回看胡正明的工作其實並不復雜,他只回答了一個問題:漏電流會從哪裏經過呢?你可能會問,這有什麽值得研究的,既然導通時電流從導電溝道經過,漏電不也該發生在這裏嗎?

還真不是。

胡正明給出了一個不一樣的結論——經過計算和模擬,漏電發生的位置比人們猜想的更深。就像下方的示意圖,顏色越紅,代表電流密度越大,可以看到漏電發生在更深的地方,而不是導電溝道附近。

所以之前的科學家努力的方向好像都不太對,如果漏電發生在深處而不是表面,將絕緣體做薄,柵極有用的訊號確實會距離漏電的地方更近一些,但已經不足以和幹擾拉開差距,再薄的氧化物也鞭長莫及。

於是一個更離譜的想法誕生了。漏電發生在半導體深處,那如果更深的地方沒有半導體存在,漏電流不久也跟著消失了嗎?

把這個看似天真到有點傻的辦法轉變成正經的科學研究就是這樣:

下圖的三個半導體,從右到左,越來越薄,圖中的顏色越綠、越藍,代表漏電流越小。

漏電,只要足夠薄就能解決。但是,在三維軟體中將一塊半導體變薄十分簡單,在現實中卻極其復雜,並且十分昂貴。怎樣把這個薄薄的東西造出來,還要保證足夠便宜呢?——一個詭異的想法在胡正明的大腦中誕生。

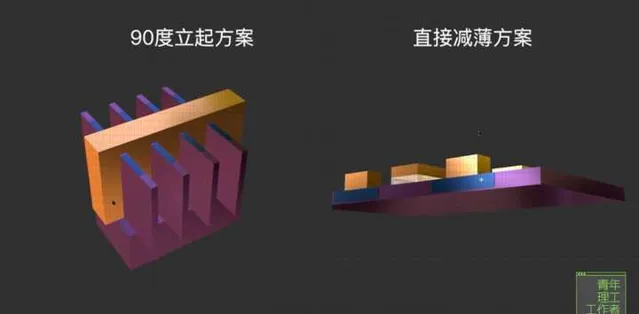

還是原來厚厚的平面型晶體管,如果能把上面這一層掀起來,掀個 90 度,立在矽表面,一個超薄晶體管就形成了。只不過這個超薄晶體管是立著放的。源極、漏極、柵極、導電溝道,還和原來一樣。

這個尺寸,也就是晶體管的厚度,決定了漏電流的大小。像現在這麽薄時,漏電流就可以忽略了。

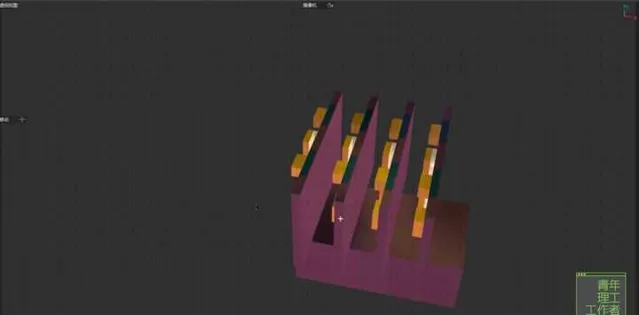

這種方案,還能在有限空間內放下更多的超薄晶體管。我們可以把這個薄片復制幾份,像這樣一起立在矽上。

既然晶體管已經立起來了,它們的柵極和其他金屬也要找個新位置。只需要直接蓋上一條金屬,當做它們共同的柵極,4 個立起來的晶體管就完成了。令人難以置信的是,造這樣一個奇葩的結構,要比直接減薄的方案更便宜,也更容易。

要理解這個反常的結論,我們首先要探尋厚厚的老式平面型晶體管其中的一個細節——STI(Shallow Trench Isolation淺槽隔離)。這個名稱其實還挺形象的,其實就是在矽片上挖許多槽,用絕緣的氧化物填滿。厚厚的老式平面型晶體管生長在這些槽之間。這樣一來絕緣槽就能將晶體管隔離起來,防止兩個晶體管之間相互幹擾。

既然已經挖槽了,那麽挖的稍微密一些,深一些,在工藝上也不會太難做。於是,一個個高高立起的薄片形成了。

仔細看,如果你不把挖下去的地方當成槽,而是把這個突起的薄片當成一個立著的薄晶體管,胡正明的想法就實作了,還是我們熟悉的柵極、源極、漏極,而導電溝道在這裏。這裏越薄,漏電流就越小到可以忽略。

立起來的一個個超薄晶體管如同魚鰭,人們給它起了一個形象的名字——FinFET,鰭式場效應晶體管。

FinFET 的想法在 1999 年誕生,十年後,平面型晶體管進入 32nm 的時代,正如當初的預言,這已經是平面型晶體管的極限。2011 年,第一批使用 FinFET 工藝的處理器問世,人們終於突破了 30 nm的魔咒,進入了 20 nm的時代。

回到題主的問題,在30nm以前的時代,我們確實可以說,數位越小,很大程度代表芯片的效能越好。但此後廠家宣傳的 22 nm、14 nm、7 nm、3 nm,都不再代表導電溝道的尺寸。由於標準不一樣,這些數位所衡量的位置沒有統一的標準,很難說3nm就一定比5nm更先進。不過,隨著尺寸進一步減小, FinFET 也相繼出現了漏電以及漏電意外的其他問題,FinFET 的尺寸極限也許並不遙遠,這會是物理制程的天花板嗎?