說一下我的理解。

之所以需要設計電路,很明顯是為了實作某種需求。

比方說,我要聽音樂。

那麽,除了喇叭外,我們必須準備一塊電路板。也就是需要設計並制作一塊路線板。在這裏我們只談設計。

第一步是確定詳細的需求。

舉例:

1、我要求電路可以使喇叭最大功率達到10瓦特(W);

2、我要求喇叭輸出10W的功率時,放大器失真(也就是THD)不超過0.5%;

3、我要求放大器的頻率至少能工作在20Hz至20KHz。

有了這三個需求後。

便可以進行設計 電路架構 了。

這也是最重要的一步。 電路架構的設計。

就像建造房子,先澆築框架,然後細化。

還是以音訊放大器舉例。

先計算當輸出功率為10W時,流過喇叭的電流I=1.12A。(假設負載為8Ω;1KHz)

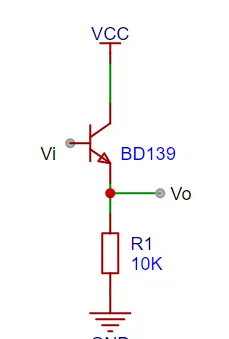

由於需要流過這麽大的電流,在晶體管的三種基本接法中,只能選擇集電極接地電路。也就是常說的發射極跟隨器。

如下圖:

此時電壓為Vo=1.12*8=8.96V。

而CD機出來的訊號有兩個特點。一是有效值約2V;二是輸出阻抗相對較大。(且CD機訊號末尾一般有隔直流電容)

所以,需要把CD機出來的音訊訊號的電壓放大到8.96V。

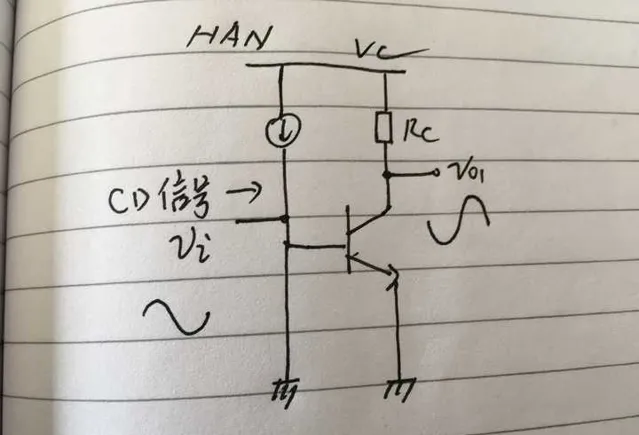

此時可以選擇共基或共射電路。但由於音源輸出電阻較大,而共基電路輸入電阻較小。所以只能選共射電路。

如下圖:

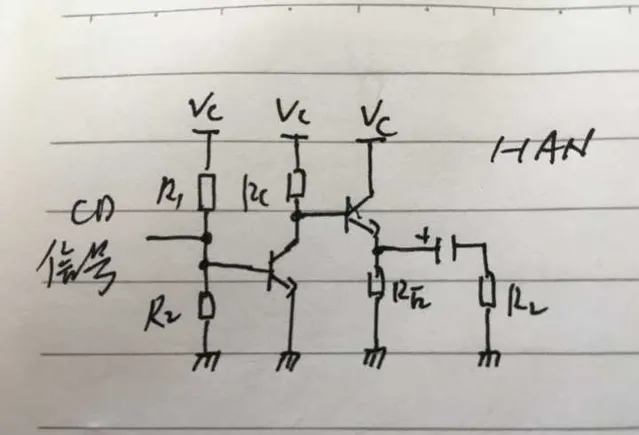

那麽,電路的基本架構也就成型了。如圖:

第三步是對架構進行調整。

分析第二步架構中存在哪些問題 。

比方說上面這個架構,我們分析一下他的缺點:

1、跟隨器的空載電流較大(空載電流需要遠大於1.12A,否則波形負半周必定會削波),造成發熱嚴重且放大器效率低下,如果要解決這個問題必須接上非常大的熱沈(散熱板);

2、輸出級使用了電容,會和負載形成高通濾波器,但如果降低HPF所造成的影響,勢必需要使用大容量電解電容,增加了較多成本不說,可靠性也會降低;

3、這個電路的溫漂會很嚴重。

4、這個電路的失真會很大。

根據這四個缺點,我們進行架構的調整。

1、空載電流較大,所以必須修正為推挽跟隨器電路;同時可以解決使用輸出電容的問題;

2、對初級電路使用差動放大電路,改善溫漂的情況;(以犧牲一個三極管為代價)

3、關於失真的問題,可以增加開環增益(使用恒流源、采用多級放大等),然後進行深度負反饋配置,可以大幅降低THD和雜訊;

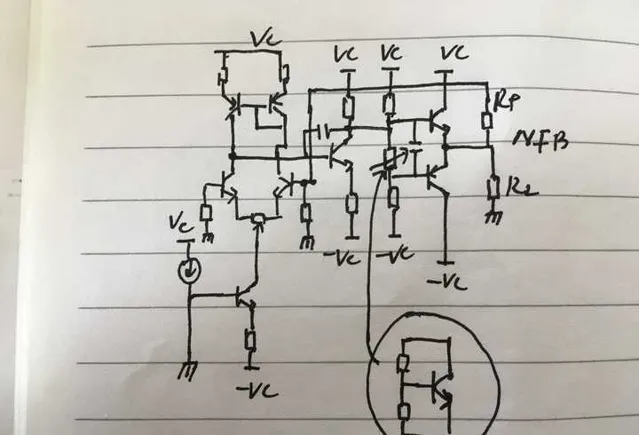

調整後的架構如圖:

架構確定後,就是 具體設計 了。簡單來說,就是 確定架構中每一個元器件的具體參數、型號。

這一步也是相當關鍵的。對於本圖中,我們可以先進行人為計算(估算,即把基射壓降固定看做0.65V),利用歐姆定律即可。然後進行微調整。

此時我們可以說電路原理圖已經 基本設計完畢 。接下來一般會進行仿真,一般使用LTSPICE或者Multisim10.0。

把原理圖確認無誤後,輸入到AD、PADS等EDA軟體,即可著手進行路線板LAYOUT的設計了。

有關PCB布局(LAYOUT)的設計又是相當關鍵的一個步驟。尤其是高頻路線板或者超高速電路。在高頻電路中,就算原理圖設計的再好再精確,不懂布局設計的話,訊號會發生很多奇怪的現象。

當然,高頻電路(RF)的拓撲也和低頻有很大的區別。這點我會放在最後面進行一些細節描述。

以上是模擬電路設計的基本思路。

對於數位IC電路,則是完全不同的所謂的HDL設計方法。也就是硬體描述語言。主流的有Verilog語言。通俗的說就是利用電腦設計路線。設計人員只需要提出需求,接下來就完全交給編譯器。

比方說:

module test(

input a;

input b;

output c;

);

assign c=a^b;

endmodule

編譯器很快辨識出這是一個異或門。

畢竟大規模數位電路過於復雜,只能借助電腦。

後續我會寫一個實際的例子來表明如何對數位電路進行設計。

更新一些東西。

上次寫的時候對電路框架進行了簡單的介紹,而關於 元件的具體設計 沒怎麽說。

本次更新寫一下電路具體設計時需要註意的地方。

電路架構確定後,需要對每一個元器件進行計算,從而確定每個元件的額定參數。

舉個例子:

示波器是一個很常見的儀器,被譽為 電子工程師的眼睛。

示波器的最重要的配件便是探頭。一般隨機配備的探頭都是具有10:1和1:1兩種衰減比。

最大測量電壓一般不超過數百伏。(典型值300Vrms,10:1衰減)

如果要測量高壓訊號(如一些高壓脈沖),顯然隨機的標配探頭是不能進行測試的。

而裝置公司售賣的專用高壓探頭往往是相當昂貴的。

以T公司售賣的無源高壓探頭為例,價格往往為四位數。

示波器用高壓無源探頭其本質為頻率特性較好的衰減器。(而萬用表的衰減器雖然可能衰減比達到了要求,但頻率特性不滿足)

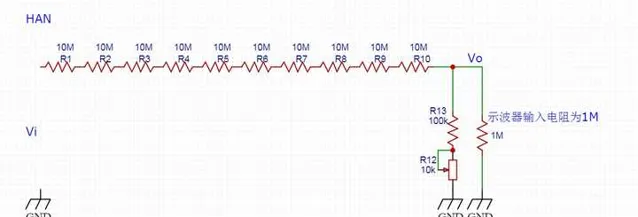

如果是為了省錢而要自制探頭的話,我們設計了下圖的電路原理圖。

當訊號最高電壓為20KV時,示波器上的電壓為20V,此時把示波器內探頭衰減比調為1000:1,螢幕上可以觀察到相應波形。

下面確定具體的元器件型。

R1至R10上的總壓降為20000/1001*1000≈20KV;每個10M電阻的壓降為2000V;

那麽每個電阻功率為P=U²/R=0.4W。

那麽我們選擇1W(取一倍的余量)的金屬膜(或碳膜)電阻便可以了嗎?

結果是自制的高壓探頭會被炸掉。

原因是我們只考慮了電阻的額定功率,而忘記了考慮其他的參數是否滿足要求。

在本例中,未考慮的參數是電阻的額定電壓。

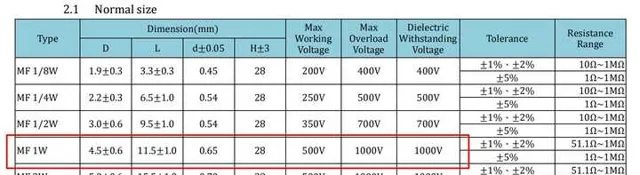

我們看下圖U公司的電阻DATASHEET。

我們可以看到1W電阻額定電壓只有500V,而絕緣耐受電壓為1000V。所以加上2KV的電壓時,電阻會被擊穿,導致電阻短路,自制的高壓探頭自然就BOOM了。(實際情況可能會看到一些「劈啪」的小火花和爆鳴聲)

而實際電路制作時,分壓電阻必須加上補償電容,大小視示波器的輸入電容而定。假定示波器輸入電容為30pF,那麽補償電容一般設定為30fF。(這種電容應該買不到,所以實際電路中需要串聯多個電容,以形成這麽小的電容)否則會因為示波器自身輸入電容的緣故導致無法使用。