英特爾為什麽還在用14nm,最大的原因就是10nm翻車了,這個相信大家也都知道的。10nm翻車的主要原因,在技術上真的就是選擇了過於激進的方案,按照原始的,選擇在2016年用DUV去實作別廠EUV的密度,還塞一堆新技術在裏面。

在Intel研發10nm的時間點(按照計劃16-17年登場),EUV還是不可用的(2019年底),這個時候Intel就必須選擇其它手段來規避這個問題。兩種選擇,降低10nm的技術標準,和台積電7nm一樣選擇在SADP的範圍內,或者上SAQP四重曝光。可能是想著順手解決7nm的量產問題,Intel激進的選擇了SAQP,還有一堆新技術,最後導致良品率一直有問題上不去,所以10nm根本不堪用,只能打磨14nm。

除了工藝問題,還有另外一個原因,那就是Intel沒有用10nm的決心。Intel在2019年的Icelake上已經解決了10nm造消費級核心的能力(100多的面積),Intel其實完全可以做8核心的Icelake S,和AMD一樣走低頻多核心路線。按照Icelake SNC高18%的IPC,Icelake S如果有的話跑個4.1G也還勉強。Intel顧及絕對效能(目前來看可能不如9900K),也沒有用。

但為什麽要說Icelake S,因為Intel現在在TGL和ICL SP上似乎又遇到良品率問題了,可能又要延遲了,Intel在自己10nm的生產上經驗還不足的問題暴露。如果當時Intel在桌面級混用Icelake S和CFL S,或者移動端直接砍了CML U全靠ICL U,靠大規模的出貨量和生產經驗打磨10nm,或許今天TGL ICL SP這樣要求比較高的核心問題就不太大了。

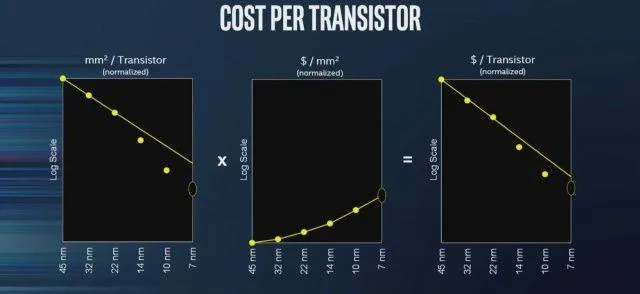

所以Intel顧及10nm成本問題(Intel今年年中利潤說要降 因為10nm更多量產了,Intel也多次聲明這個貴,特別是再對比用很久的14nm)、絕對效能問題,導致經驗不足也是至今用不上的因素之一。

而且很不幸的是,Intel這個不好的勢頭還在繼續,TGL U的面積可以做TGL H了(核顯換CPY),頻率4.8G也夠了,Intel不一起發。那好等5.0G的TGL H,這也夠桌面了吧,AMD 4000也難幹到5.0G且相同IPC,抱歉也沒有。Intel還是選擇穩妥的路子,照顧當前的成本,給未來埋坑。

最最最後,Intel死腦筋。10nm大芯片良率有問題,這給可以預期到的,自家早早有那麽多先進封裝的工藝,為啥不考慮下和AMD一樣試試膠水呢?

----

更新:根據最新財報公開顯示,10nm計劃部份,Tiger Lake就是Q3推出,這個和最新傳聞符合,9-10大面積鋪貨。Icelake SP年底,至少比查理說的要快。Alder Lake目前說的是2021p,而且提到了桌面版,這個比之前預期要略高一些。第二代10nm Xeon Sapphire Rapids也正常: