之前很長一段時間內CPU都在堆核,但現在堆核也到了瓶頸。但CPU的發展不會停止,以下幾個方面還有潛力可以挖掘:

工藝、架構(DSA、並列、緩存)、材料、異構、封裝、Chiplet、SoC、AI(NPU)

從突破性的技術來看,有以下兩個方面:

量子芯片、碳基芯片

工藝

工藝依然是未來5-10年影響CPU效能的一個非常重要的方向。我在之前裏的回答寫過,雖然晶體管在10nm以下會出現短溝道效應和量子遂穿效應,但我們依然可以在晶體管12nmGate Length下實作等效2nm的單位晶體管密度。

工藝方面的現狀是目前5nm已經實作量產,3nm已經在研發的路上了,目前主要是台積電和三星兩家Foundry。

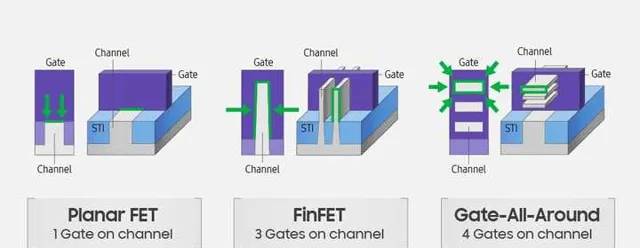

三星的3nm工藝會使用環繞柵極晶體管(GAA)技術,而不是現在的FinFET,新的技術可以讓芯片面積減少35%,功耗下降約50%,與5nm FinFET工藝相比,同樣功耗情況下效能提升33%。

GAA全能門與FinFET的不同之處在於,GAA設計圍繞著通道的四個面周圍有柵極,從而確保了減少漏電壓並且改善了對通道的控制,這是縮小工藝節點時的基本步驟,使用更高效的晶體管設計,再加上更小的節點尺寸,和5nm FinFET工藝相比能實作更好的能耗比。

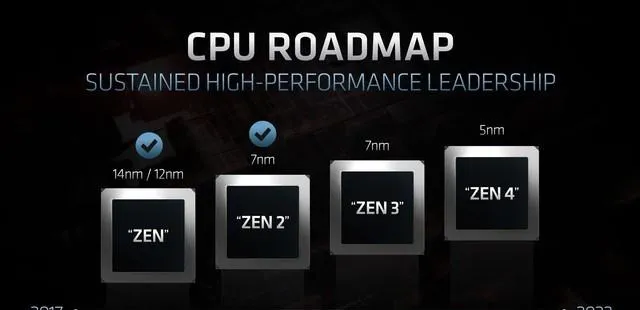

而台積電依然采用FinFET,預計2022年下半年台積電3nm工藝就會投產。蘋果作為台積電最重要的客戶,肯定會獨占一段時間的產能,其他客戶包括英特爾、賽靈思、輝達、AMD等。

架構

架構是未來CPU除工藝外最重要的方向之一!架構對一個芯片的效能來說也是至關重要的。

相較於X86通用處理器的笨重指令集,DSA(Domain Specific Architecture)是一個非常重要的方向。DSA的優點在於,可以為特定的一類套用或者場景做架構最佳化,從而實作更好的能效比。相對於傳統的通用處理器,DSA需要設計時考慮專用領域的特殊需求,也需要設計者能對該領域有深入的理解。DSA的例子包括為機器學習設計的神經網路處理器,以及為影像和虛擬現實設計的GPU,DSA設計將會成為處理器架構的新趨勢。

當然,除了指令集外,多執行緒並列和緩存也很重要! 以AMD的Zen架構舉例,利益相關,所以放一點百度上有的。

Zen架構將以四個核心為一個群組,AMD將其稱為「CPU Complex」(CCX)。

每一個CPU復合體內包含四個Zen CPU核心,但它們是彼此完全獨立的,不像推土機架構那樣,彼此不會共享任何單元。

處理器主要架構改進如下 :

·SMT多執行緒,每個核心可支持2個執行緒

·8MB L3緩存

·容量更大、更統一的L2緩存

·微操作緩存(Micro-op Cache)

·具備2個AES加密單元

·高能效FinFET工藝

「Zen」核心采用了最新緩存階層,並改進了分支預測和同步多執行緒技術 [4] 。這些先進設計將使「Zen」處理器核心極具彈性,以滿足廣泛的套用需求,其中包括無風扇2合1產品、嵌入式系統、高效能計算和數據中心。

材料

半導體行業經過近六十年的發展,半導體材料經歷了三次明顯的換代和發展。第一代半導體材料主要是指矽、鍺元素等單質半導體材料;第二代半導體材料主要是指化合物半導體材料,如砷化鎵、銻化銦;第三代半導體材料主要分為碳化矽SiC和氮化鎵GaN,相比於第一、二代半導體,其具有更高的禁頻寬度、高擊穿電壓、電導率和熱導率,在高溫、高壓、高功率和高頻領域將替代前兩代半導體材料。 [1]

碳化矽(SiC)相比於矽基,碳化矽擁有更高的禁頻寬度、電導率等優良特性,更適合套用在高功率和高頻高速領域,如新能源汽車和 5G 射頻器件領域。

隨著芯片在不同領域的套用,半導體材料也在隨之發展。但如果扣回本題,新材料在CPU上套用機率很小。

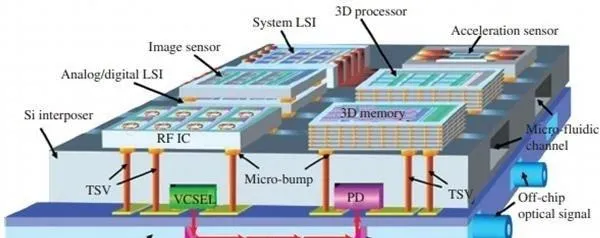

異構整合

廣義而言,就是將兩種不同的芯片,例如記憶體+邏輯芯片、光電+電子元件等,透過封裝、3D 堆疊等技術整合在一起。換句話說,將兩種不同制程、不同性質的芯片整合在一起,都可稱為是異構整合。

因為套用市場更加的多元,每項產品的成本、效能和目標族群都不同,因此所需的異構整合技術也不盡相同,市場分眾化趨勢逐漸浮現。為此,IC 代工、制造及半導體裝置業者紛紛投入異構整合發展,2.5D、3D 封裝、Chiplets 等現今熱門的封裝技術,便是基於異構整合的想法,如雨後春筍般浮現。

封裝

封裝並不能直接提高芯片的效能,但是先進的3D封裝工藝相較於傳統的2D工藝有很多優勢:

台積電的Wafer-on-Wafer(WoW) 3D芯片封裝工藝,是透過TSV矽穿孔技術實作了真正的3D封裝,和Intel的Foreros 3D封裝類似,能把多個芯片像蓋房子那樣一層層堆疊起來,甚至能把不同工藝、結構和用途的芯片封在一起。

TSV也是非常火的技術,要知道數據的搬運速率對CPU效能的影響是非常大的。

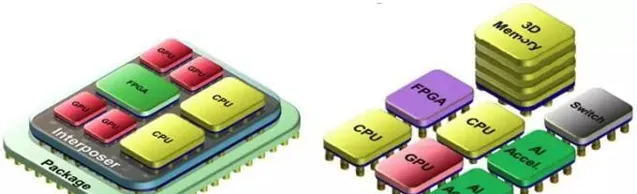

Chiplet

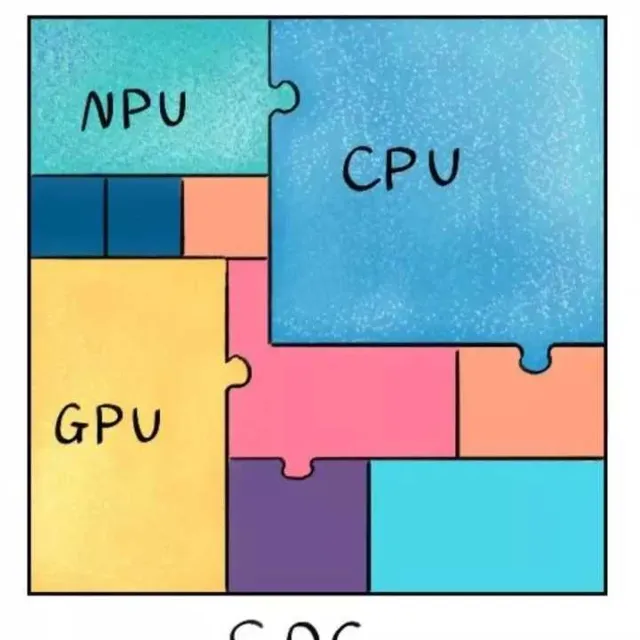

Chiplet技術就像拼圖一樣,把小芯片組成大芯片。

使用Chiplets 有三大好處。因為先進制程成本非常高昂,特別是模擬電路、I/O 等愈來愈難以隨著制程技術縮小,而Chiplets 是將電路分割成獨立的小芯片,並各自強化功能、制程技術及尺寸,最後整合在一起,以克服制程難以微縮的挑戰。

此外,基於Chiplets 還可以使用現有的成熟芯片降低開發和驗證成本。

從上面的分析也可以看出來,異構-chiplet-封裝也是相輔相成,共同發展的。

SoC

SOC(System-On-Chip), 即片上系統。可以簡單的理解為把系統做在一塊芯片上。

一個完整的SoC通常包含以下幾個模組:

中央處理器(CPU)-- SoC的「大腦」。執行Android 或者IOS和大多數應用程式的大部份程式碼。

圖形處理單元(GPU)-- 處理與圖形有關的任務,例如視覺化應用程式的使用者介面和2D、3D遊戲。

影像處理單元(ISP)--將手機網路攝影機中的數據轉換為影像和視訊檔,對影像用AI演算法進行進階處理。

數位訊號處理器(DSP)-- 處理比CPU更復雜的數學功能。包括解壓縮音樂檔和分析陀螺儀傳感器數據。

基頻處理單元BBU(Building Base band Unite)—用於網路覆蓋。

記憶體(ROM/RAM)-- 用來儲存程式和各種數據資訊的記憶部件。記憶體可分為主記憶體(簡稱主記憶體或記憶體)和輔助記憶體(簡稱輔存或外存)兩大類。和CPU直接交換資訊的是主記憶體。

神經處理單元(NPU)-- 用於高端智慧型手機,以加速機器學習(AI)任務。這些包括語音辨識和相機處理。

除了以上幾個主要單元,還有藍芽,5G,WI-FI等模組。

SOC技術可以有效地降低電子資訊系統產品的開發成本,縮短開發周期,提高產品的競爭力,是未來工業界將采用的最主要的產品開發方式。

AI芯片

也就是人工智慧芯片,上面再SOC裏已經提到了,NPU用於加速神經網路的運算,解決傳統芯片在神經網路運算時效率低下的問題。

除了NPU,還有TPU(Tensor Processing Unit)即張量處理單元。

如圖是一款為機器學習而客製的人工智慧處理器。經過了專門深度機器學習方面的訓練,它有更高的計算能力。TPU在經過深度學習方面的訓練,執行每個操作所需的晶體管數量更少,自然效率更高。

從突破性的技術來看,主要有量子芯片和碳基芯片。

相對來說,這兩種技術目前還處在實驗室研發階段,距離商用尚遠,從目前的資訊來看,順利的話,量子芯片要十年甚至更久,碳基芯片也要五年左右。

莫耳定律(我認為叫莫耳規律更恰當)放緩,CPU的效能並不會走到盡頭。人們為了對抗莫耳定律的失效,不斷在研發新技術、新架構、新材料為莫耳定律續命,同時也在不同的方向進行探索,CPU這個跨越世紀的重器,也將在未來十年煥發新春。

參考

- ^https://dy.163.com/article/FSEJSJ2B051481OF.html