編輯:編輯部 HYZ

【新智元導讀】英特爾至強6效能核處理器加速推理達2.4倍,可謂是獲得了業界的一波關註。透過深入分析其架構,核數、記憶體頻寬大幅提升的加持可謂功不可沒。也正因此,至強6得以推理效能激增,進一步提升了推理性價比。而推理成本正是大語言模型落地最後最關鍵的挑戰。

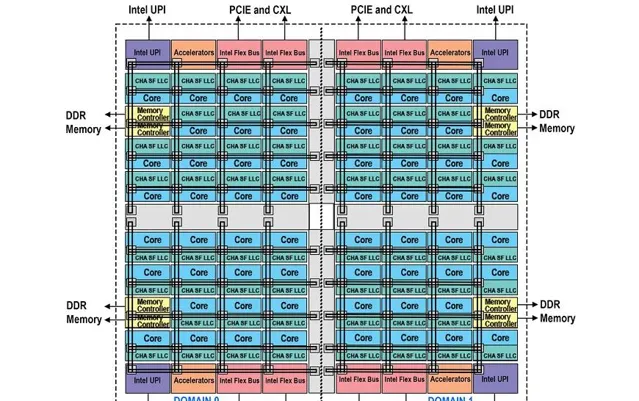

之前的文章中,有業者預測至強6效能核處理器每顆計算單元芯片中的內核數量為43,加上每個計算單元有兩組雙鍊結記憶體控制器各占一個網格,那麽總共占用43+2=45個網格,可以由5×9的布局構成。

但這個假設有一個問題,要構成128核的6980P,三顆芯片只遮蔽1個內核,這良率要求比較高啊。

至今還未在公開渠道看到至強6效能核處理器的Die shot或架構圖,但英特爾釋出了晶圓照片作為宣傳素材。

雖然晶圓照片並不能提供每顆芯片的清晰資訊,但隱約能感覺到,網格構成更像是5×10,而不是5×9或6×8。

另外,左上角和左下角疑似記憶體控制器的區域面積比預想的要大得多,每一側占了三個網格。

如果接受了兩組記憶體控制器共占用6個網格的設定,那麽每個芯片中就是50-6=44個內核,在構成6980P的時候分別遮蔽一到兩個核即可,感覺就合理多了。

在獲得相對可信的內核數量後,新的疑惑就是:為什麽至強6效能核的記憶體控制器這麽占地——這個區域有其他未知功能?還是因為增加了MRDIMM(Multiplexed Rank DIMM)的支持?

畢竟在此之前,英特爾的雙鍊結DDR5、三通道DDR4記憶體控制器只占一個網格,甚至,連訊號規模更大、頻寬更高的HBM控制器(至強CPU Max處理器)也是一個網格。

至強CPU Max處理器的HBM2e是工作在3,200MT/s,那麽每個控制器頻寬是410GB/s,整顆CPU有超過2TB/s的HBM頻寬。

雖然對疑似記憶體控制器區域所占芯片面積的疑惑未解,還需要進一步解惑,但我們至少可以確定,英特爾在這一代至強的記憶體控制器上是下了大本錢的。

至少在相當一段時間內,它是可以「獨占」MRDIMM的優勢了。

至強6效能核的NUMA與集群模式

談伺服器的記憶體就繞不過NUMA(Non-Uniform Memory Access,非統一記憶體存取)。因為隨著CPU內核數量的增加,各內核的記憶體存取請求沖突會迅速增加。

NUMA是一個有效的解決方案,將內核分為若幹組,分別擁有相對獨立的緩存、記憶體空間。規模縮小後,沖突就會減少。

一般來說,NUMA劃分的原則是讓物理上臨近某記憶體控制器的內核為一個子集。這個子集被英特爾稱為SUB-NUMA Clustering,簡稱SNC。同一SNC的內核繫結了末級緩存(LLC)和本地記憶體,存取時的時延最小。

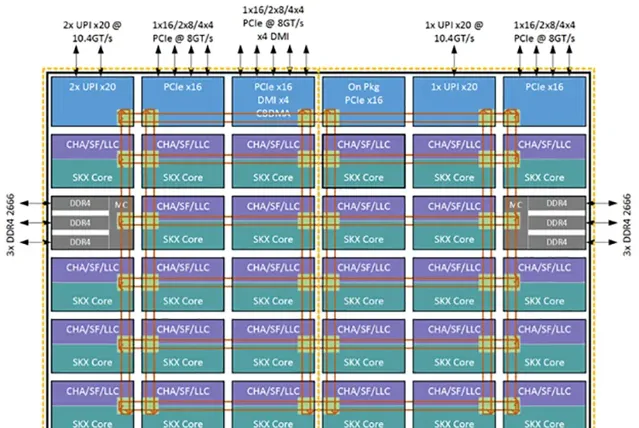

譬如,在第三代至強可延伸處理器中,一個CPU內可劃分兩個SNC域,每個SNC對應一組三通道DDR4記憶體控制器。如果關閉NUMA,那麽整個CPU的記憶體將對稱存取。

而第四代至強可延伸處理器使用了4顆芯粒的封裝,可以被劃分為2個或4個SNC域。

如果希望每個內核可以存取所有的緩存代理和記憶體,可以將第四代至強可延伸處理器設定為Hemisphere Mode或者Quadrant Mode,預設是後者。

第五代至強可延伸處理器是2顆芯粒,可以劃分為兩個SNC域。

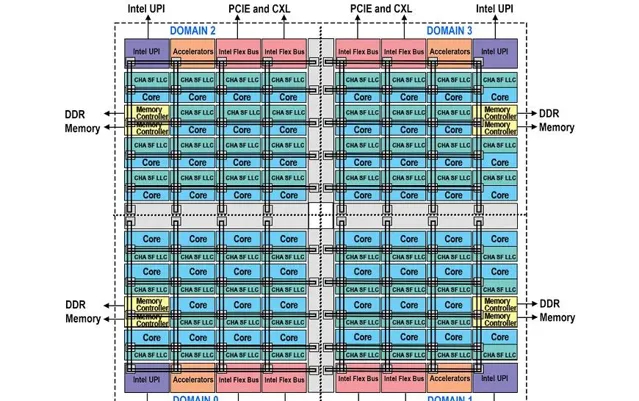

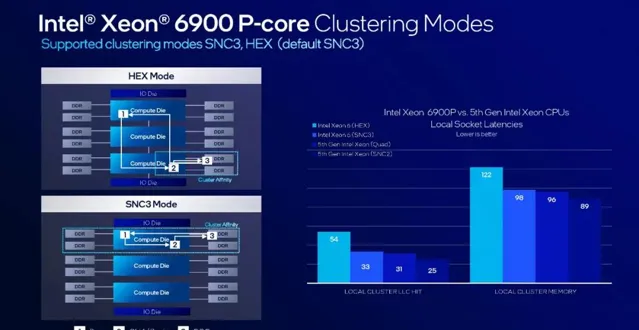

在至強6效能核中,可以將每個計算單元芯片作為一個SNC,每個域擁有4個記憶體通道,這被稱為SNC3 Mode。

如果要透過其他芯粒的緩存代理存取所有記憶體,那就是HEX Mode。

根據英特爾提供的數據,幾種不同模式的記憶體存取時延差異較大,與內核、記憶體控制器之間的「距離」直接相關。

至強6效能核的內核規模、記憶體控制器數量增加之後,相應的存取時延也會上升。

例如,根據我們前面的觀察,至強6效能核內每個計算單元芯片中,內核與記憶體控制器的最遠距離為10列,而第四代/第五代至強可延伸處理器無NUMA的為8列。這反映在英特爾的數據上,就是至強6900P在SNC3 Mode的時延略高於上一代至強處理器的Quad Mode。

如果至強6900P設為HEX Mode,那麽內核與記憶體控制器的最遠距離將達到13甚至15列,時延增加會比較明顯。

整體而言,由於SNC3 Mode時延低,其將成為至強6伺服器的預設模式。這種模式主要是適合虛擬化/容器化這類常見雲套用,以及並列化程度高的計算(如編解碼)等。

當然,HEX Mode可以直接存取更大規模的記憶體,這對於大型數據庫,尤其是以OLTP為代表的套用來說更為有利。

Oracle和SQL通常建議關閉NUMA以獲得更佳的效能。Apache Cassandra 5.0這類引入向量搜尋的數據庫也能從HEX Mode顯著獲益。部份科學計算也更適合HEX Mode,譬如透過偏微分方程式建模的PETSs、分子動力學軟件NAMD等。

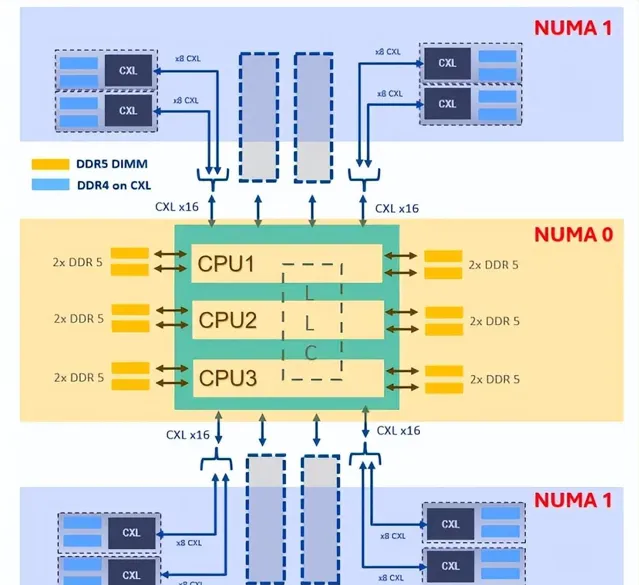

HEX Mode的另一個典型場景是配合CXL記憶體使用。

譬如英特爾在今年12月11日釋出的一篇利用CXL記憶體最佳化系統記憶體頻寬的論文中,使用了至強6900P搭配12條64GB DDR5 6400以及8個128GB CXL記憶體模組,其中至強6900P原生的768GB DDR5記憶體在HEX Mode下配置為NUMA0,所有的1TB CXL記憶體配置為NUMA1,采用最佳化交錯配置(Interleaving Strategy)。

測試表明,在記憶體頻寬敏感的套用中,使用CXL記憶體擴充套件可以提升20%~30%的效能。

MRDIMM領跑者

對於至強6效能核處理器而言,提升記憶體頻寬最直接的方法莫過於MRDIMM。這也是這款處理器相比其他同類產品比較獨占的一項能力,近期看不到任何其他CPU廠商有明確支持MRDIMM的時間表,更不要說推出實際產品了。

相對而言,記憶體廠商對MRDIMM的支持比較積極,美光、SK海力士、威剛都推出了相應的產品,包括高尺寸(Tall formfactor,TFF)。

第一代DDR5 MRDIMM的目標速率為8,800 MT/s,未來會逐步提升至12,800 MT/s、17,600 MT/s。

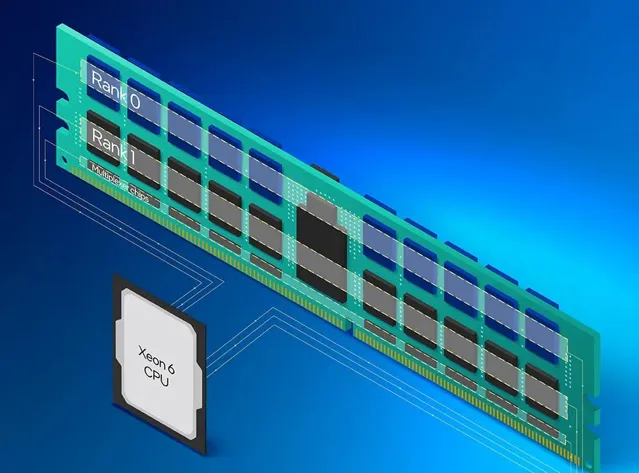

MRDIMM增加了多路復用數據緩衝區(MDB),改進了寄存時鐘驅動器(MRCD)。

MDB布置在記憶體金手指附近,與主機側的CPU記憶體控制器通訊。MDB主機側的執行速度是DRAM側的雙倍,DRAM側的數據介面是主機側的雙倍。

MRCD可以生成4個獨立的芯片選擇訊號(標準的RCD是兩個,對應兩個Rank)。

MDB可透過兩個數據介面將兩個Rank分別讀入緩沖區,再從緩沖區一次性傳輸到CPU的記憶體控制器,由此實作了頻寬翻倍。

由於MRCD可以支持4個Rank,也意味著可以支持雙倍的記憶體顆粒。已經展示的MRDIMM普遍引入更高的板型(TFF),單條容量也由此倍增。

由於至強6900P插座尺寸大增,導致雙路機型的記憶體槽數量從上一代的32條減少到24條。要能夠繼續擴充套件記憶體容量,增加記憶體條的面積(增加高度)確實是最簡單直接的手段。

透過使用256GB的MRDIMM,雙路至強6900P機型可以獲得6TB記憶體容量。除了更大的記憶體頻寬,更高的記憶體容量也非常有利於AI訓練、大型數據庫等套用的需求,進一步強化至強6900P在AI機頭領域的優勢。

與DDR5 6,400MT/s相比,MRDIMM 8,800MT/s的實際執行頻率略低(4,400MT/s),導致輕量級的套用不能從記憶體頻寬的增加當中明顯獲益。

其實類似的問題在記憶體代際轉換之初均會存在,能夠充分利用更大記憶體頻寬的主要還是計算密集的套用,譬如加密、科學計算、訊號處理、AI訓練和推理等。從目前的測試看,對MRDIMM受益最大的套用主要包括HPCG(High Performance Conjugate Gradient)、AMG(Algebraic Multi-Grid)、Xcompact3d這些科學計算類的套用,以及大語言模型推理。

記憶體頻寬與大模型推理

上一節有提到,並非所有套用都能充分利用MRDIMM的記憶體頻寬收益。

就本節重點要談的推理套用而言,根據目前所見的測試數據,摺積神經網絡為代表的傳統推理任務在MRDIMM中獲得的收益就比較小,不到10%的水平。

而在大語言模型推理當中,MRDIMM的頻寬優勢將得到充分的發揮,效能提升在30%以上,因為大模型是確定性的渴求視訊記憶體/記憶體容量和頻寬的套用場景。

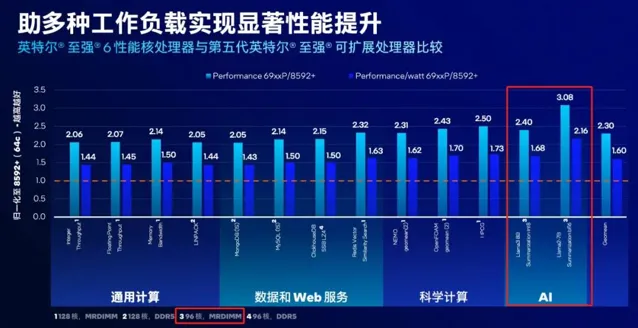

在這裏就得提一下英特爾至強6效能核處理器釋出會資料中的另一個細節:在多種工作負載的效能對比中,AI部份的提升振幅最為明顯,而且僅用了96核的型號(至強6972P)。

也就是說,至強6972P使用了至強8592+的1.5倍內核,獲得了至少2.4倍的大語言模型推理效能。其中,右側的是Llama3 8B,int8精度,那麽模型將占用約8GB的記憶體空間。

以目前雙路24通道MRDIMM 8,800MT/s約1,690GB/s的總記憶體頻寬而言,可以算出來每秒token數理論上限是211。

而雙路8592+是16通道DDR5 5,600MT/s,記憶體總頻寬為717GB/s,token理論上限是接近90。二者的理論上限正好相差大約2.4倍。

在這個例子當中,記憶體頻寬的增長振幅明顯大於CPU內核數量的增長。也就是說,在假設算力不是瓶頸的情況下,記憶體或視訊記憶體容量決定了模型的規模上限,而頻寬決定了token輸出的上限。

一般來說,在控制模型參數量並進行低精度量化(int8甚至int5、int4)之後,大語言模型推理時的算力瓶頸已經不太突出,決定並行數量和token響應速度的,主要還是記憶體的容量和頻寬。透過MRDIMM,以及CXL記憶體擴充套件頻寬將是提升推理效能最有效的方式。

這也是目前CPU推理依舊受到重視的原因,除了可獲得性、資源彈性外,在記憶體容量及頻寬的擴充套件上要比VRAM便宜的多。

結語

隨著掌握更多的資訊,至強6效能核處理器在記憶體頻寬上的優勢和潛力顯得愈發清晰了。

MDRIMM不但能夠大幅提升記憶體頻寬,還能使可部署的記憶體容量翻倍,顯著利好傳統的重負荷領域,如科學計算、大型數據庫、商業分析等,對於新興的向量數據庫也大有裨益。CXL還能夠進一步起到錦上添花的作用。

過去幾年,增長迅猛的大模型推理需求,讓至強可延伸處理器(從第四代開始)利用GPU缺貨的契機證明了在AMX的加持下,純CPU推理也有不錯的效能,而且易於采購和部署。

隨著套用深入,部份互聯網企業還挖掘了CPU推理的資源彈性,與傳統業務同構的硬件更易於進行峰谷排程。

至強6效能核處理器在核數、記憶體頻寬均大幅提升的加持下,推理效能激增,進一步提升了推理的性價比。

在解決了「能或不能」的問題之後,推理成本是大語言模型落地後最關鍵的挑戰。或許在這方面,至強6效能核處理器配MRDIMM的組合,將會帶來一些新的解題思路。