一. 先說單核效能:是的。

過去這些年中,單核效能的增長可以主要歸功於以下2個方面:(1)處理器微結構(MicroArch)的發展。流水線、亂序執行、分支預測這些技術使得時間上和空間上,對電路的利用更加充分。(2)CMOS工藝的發展。更小的尺寸為計算部件帶來了更低的延時、更低的功耗,為儲存部件帶來了更大的容量。

然而,(1)和(2)兩個方面的發展速度都已放緩。對於 (1) ,微結構(MicroArch)的爆發增長期是在1985年——2002年,許多革命性的技術在這一時期被套用,2002年以後技術趨於成熟,發展速度放緩。對於 (2) ,拋開能不能制造出尺寸更小的CMOS元件這個問題不談,即使可以制造出,功耗這一因素已經無法忽略。在 @逸之 的答案中已經詳細說了物理方面的因素,我這裏再就量子的影響展開說,CPU的功耗可以粗略計算為: P_{total}=CV^{2}f+P_{static}+P_{transient} ,在數百nm到數十nm的時代,占功耗大頭的是 CV^{2}f ,但是隨著工藝的不斷縮小,靜態功耗 P_{static} 占比越來越大。造成這種影響一個因素是,柵極上方的氧化層(柵氧)越來越薄,這一區域理想的功能是一個絕緣層,但現在厚度柵氧已經接近原子尺度,電子有一定機率會穿過,從而產生漏電流。

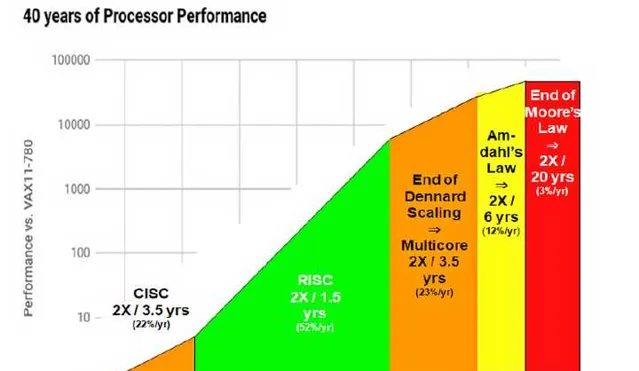

以上因素共同作用的結果就是效能增長的放緩。1980年——2004年,單核效能的進步速度約為每年52%,2005年——2012年約為每年20%,2015年——2019年約為每年3%。

二. 再說多核效能

我們可以將並列分為3類:(1)指令級並列instruction level parallel 簡稱ILP (2)數據級 data instruction level 簡稱DLP (3)執行緒級並列 thread level parallel 簡稱TLP。單核中主要利用的是ILP,ILP是所有3類中最好用的,所有程式都可以使用,並且對程式設計師透明,只需把工作丟給硬體。但剩下兩類卻沒那麽好用, 不是所有程式所有演算法都可以發掘出並列的空間 。也就是說,一個速度為2的處理器,和兩個速度為1的處理器是不一樣的。

正文至此

以下內容給非cs、ee專業的同學補充一下背景知識,cs、ee專業的同學請跳過。

- 指令集架構(ISA)和微結構有什麽區別? x86架構、ARM架構、MIPS架構說的是指令集架構(ISA),它是軟體和硬體的介面,規定了軟體和硬體的交流方式,但是處理器具體的實作與ISA無關。微結構決定了處理器具體的實作,包括劃幾級流水、幾發射、每級流水做什麽之類的資訊。

- 現代微處理器的物理實作方式是什麽? CMOS是現代芯片的馱馬。今天幾乎所有的數位計算電路都是由CMOS實作,但情況並非從來如此,比如早期的Intel 8080(1974年)僅采用NMOS邏輯實作。