之前很长一段时间内CPU都在堆核,但现在堆核也到了瓶颈。但CPU的发展不会停止,以下几个方面还有潜力可以挖掘:

工艺、架构(DSA、并行、缓存)、材料、异构、封装、Chiplet、SoC、AI(NPU)

从突破性的技术来看,有以下两个方面:

量子芯片、碳基芯片

工艺

工艺依然是未来5-10年影响CPU性能的一个非常重要的方向。我在之前里的回答写过,虽然晶体管在10nm以下会出现短沟道效应和量子遂穿效应,但我们依然可以在晶体管12nmGate Length下实现等效2nm的单位晶体管密度。

工艺方面的现状是目前5nm已经实现量产,3nm已经在研发的路上了,目前主要是台积电和三星两家Foundry。

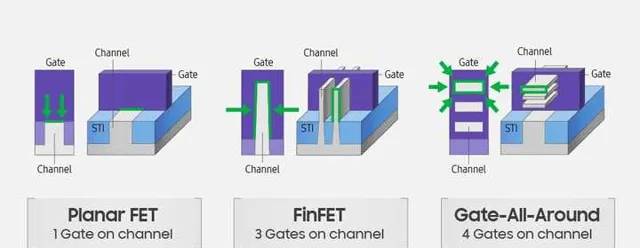

三星的3nm工艺会使用环绕栅极晶体管(GAA)技术,而不是现在的FinFET,新的技术可以让芯片面积减少35%,功耗下降约50%,与5nm FinFET工艺相比,同样功耗情况下性能提升33%。

GAA全能门与FinFET的不同之处在于,GAA设计围绕着通道的四个面周围有栅极,从而确保了减少漏电压并且改善了对通道的控制,这是缩小工艺节点时的基本步骤,使用更高效的晶体管设计,再加上更小的节点尺寸,和5nm FinFET工艺相比能实现更好的能耗比。

而台积电依然采用FinFET,预计2022年下半年台积电3nm工艺就会投产。苹果作为台积电最重要的客户,肯定会独占一段时间的产能,其他客户包括英特尔、赛灵思、英伟达、AMD等。

架构

架构是未来CPU除工艺外最重要的方向之一!架构对一个芯片的性能来说也是至关重要的。

相较于X86通用处理器的笨重指令集,DSA(Domain Specific Architecture)是一个非常重要的方向。DSA的优点在于,可以为特定的一类应用或者场景做架构优化,从而实现更好的能效比。相对于传统的通用处理器,DSA需要设计时考虑专用领域的特殊需求,也需要设计者能对该领域有深入的理解。DSA的例子包括为机器学习设计的神经网络处理器,以及为图像和虚拟现实设计的GPU,DSA设计将会成为处理器架构的新趋势。

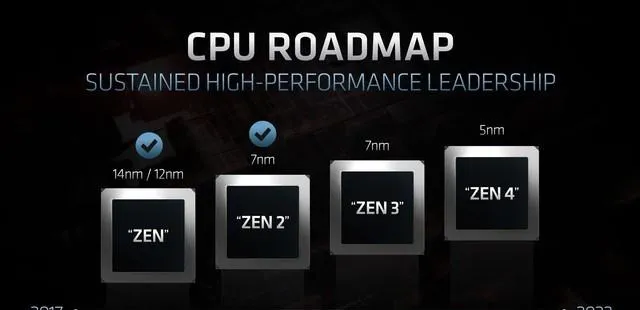

当然,除了指令集外,多线程并行和缓存也很重要! 以AMD的Zen架构举例,利益相关,所以放一点百度上有的。

Zen架构将以四个核心为一个群组,AMD将其称为「CPU Complex」(CCX)。

每一个CPU复合体内包含四个Zen CPU核心,但它们是彼此完全独立的,不像推土机架构那样,彼此不会共享任何单元。

处理器主要架构改进如下 :

·SMT多线程,每个核心可支持2个线程

·8MB L3缓存

·容量更大、更统一的L2缓存

·微操作缓存(Micro-op Cache)

·具备2个AES加密单元

·高能效FinFET工艺

「Zen」核心采用了最新缓存层次结构,并改进了分支预测和同步多线程技术 [4] 。这些先进设计将使「Zen」处理器核心极具弹性,以满足广泛的应用需求,其中包括无风扇2合1产品、嵌入式系统、高性能计算和数据中心。

材料

半导体行业经过近六十年的发展,半导体材料经历了三次明显的换代和发展。第一代半导体材料主要是指硅、锗元素等单质半导体材料;第二代半导体材料主要是指化合物半导体材料,如砷化镓、锑化铟;第三代半导体材料主要分为碳化硅SiC和氮化镓GaN,相比于第一、二代半导体,其具有更高的禁带宽度、高击穿电压、电导率和热导率,在高温、高压、高功率和高频领域将替代前两代半导体材料。 [1]

碳化硅(SiC)相比于硅基,碳化硅拥有更高的禁带宽度、电导率等优良特性,更适合应用在高功率和高频高速领域,如新能源汽车和 5G 射频器件领域。

随着芯片在不同领域的应用,半导体材料也在随之发展。但如果扣回本题,新材料在CPU上应用概率很小。

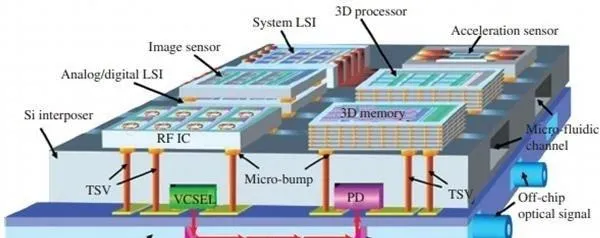

异构整合

广义而言,就是将两种不同的芯片,例如记忆体+逻辑芯片、光电+电子元件等,透过封装、3D 堆叠等技术整合在一起。换句话说,将两种不同制程、不同性质的芯片整合在一起,都可称为是异构整合。

因为应用市场更加的多元,每项产品的成本、性能和目标族群都不同,因此所需的异构整合技术也不尽相同,市场分众化趋势逐渐浮现。为此,IC 代工、制造及半导体设备业者纷纷投入异构整合发展,2.5D、3D 封装、Chiplets 等现今热门的封装技术,便是基于异构整合的想法,如雨后春笋般浮现。

封装

封装并不能直接提高芯片的性能,但是先进的3D封装工艺相较于传统的2D工艺有很多优势:

台积电的Wafer-on-Wafer(WoW) 3D芯片封装工艺,是通过TSV硅穿孔技术实现了真正的3D封装,和Intel的Foreros 3D封装类似,能把多个芯片像盖房子那样一层层堆叠起来,甚至能把不同工艺、结构和用途的芯片封在一起。

TSV也是非常火的技术,要知道数据的搬运速率对CPU性能的影响是非常大的。

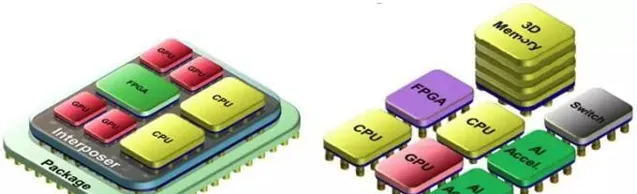

Chiplet

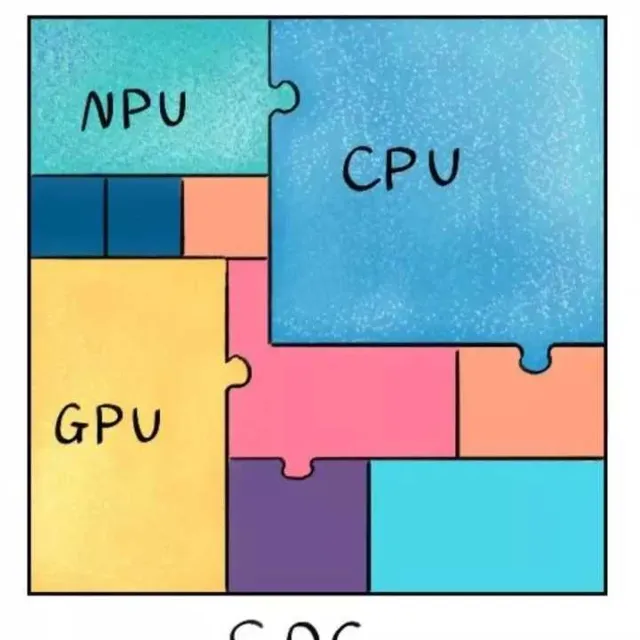

Chiplet技术就像拼图一样,把小芯片组成大芯片。

使用Chiplets 有三大好处。因为先进制程成本非常高昂,特别是模拟电路、I/O 等愈来愈难以随着制程技术缩小,而Chiplets 是将电路分割成独立的小芯片,并各自强化功能、制程技术及尺寸,最后整合在一起,以克服制程难以微缩的挑战。

此外,基于Chiplets 还可以使用现有的成熟芯片降低开发和验证成本。

从上面的分析也可以看出来,异构-chiplet-封装也是相辅相成,共同发展的。

SoC

SOC(System-On-Chip), 即片上系统。可以简单的理解为把系统做在一块芯片上。

一个完整的SoC通常包含以下几个模块:

中央处理器(CPU)-- SoC的「大脑」。运行Android 或者IOS和大多数应用程序的大部分代码。

图形处理单元(GPU)-- 处理与图形有关的任务,例如可视化应用程序的用户界面和2D、3D游戏。

图像处理单元(ISP)--将手机摄像头中的数据转换为图像和视频文件,对图像用AI算法进行进阶处理。

数字信号处理器(DSP)-- 处理比CPU更复杂的数学功能。包括解压缩音乐文件和分析陀螺仪传感器数据。

基带处理单元BBU(Building Base band Unite)—用于网络覆盖。

存储器(ROM/RAM)-- 用来存储程序和各种数据信息的记忆部件。存储器可分为主存储器(简称主存或内存)和辅助存储器(简称辅存或外存)两大类。和CPU直接交换信息的是主存。

神经处理单元(NPU)-- 用于高端智能手机,以加速机器学习(AI)任务。这些包括语音识别和相机处理。

除了以上几个主要单元,还有蓝牙,5G,WI-FI等模块。

SOC技术可以有效地降低电子信息系统产品的开发成本,缩短开发周期,提高产品的竞争力,是未来工业界将采用的最主要的产品开发方式。

AI芯片

也就是人工智能芯片,上面再SOC里已经提到了,NPU用于加速神经网络的运算,解决传统芯片在神经网络运算时效率低下的问题。

除了NPU,还有TPU(Tensor Processing Unit)即张量处理单元。

如图是一款为机器学习而定制的人工智能处理器。经过了专门深度机器学习方面的训练,它有更高的计算能力。TPU在经过深度学习方面的训练,执行每个操作所需的晶体管数量更少,自然效率更高。

从突破性的技术来看,主要有量子芯片和碳基芯片。

相对来说,这两种技术目前还处在实验室研发阶段,距离商用尚远,从目前的信息来看,顺利的话,量子芯片要十年甚至更久,碳基芯片也要五年左右。

摩尔定律(我认为叫摩尔规律更恰当)放缓,CPU的性能并不会走到尽头。人们为了对抗摩尔定律的失效,不断在研发新技术、新架构、新材料为摩尔定律续命,同时也在不同的方向进行探索,CPU这个跨越世纪的重器,也将在未来十年焕发新春。

参考

- ^https://dy.163.com/article/FSEJSJ2B051481OF.html