開篇先打個廣告:

你的點贊加關註將是激勵我持續輸的出動力!

廣義上講,由互連線引起的所有的問題。

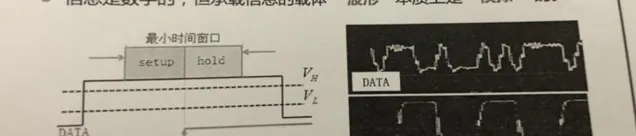

包括:時序、雜訊、電磁幹擾;簡單的理解,就是在一個周期如何分配合理時槽,使得IC能轉換成合理的數據。

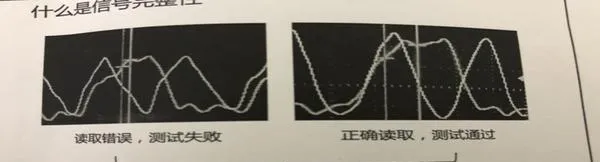

雜訊是主要要解決的問題,它包含振鈴、反射、串擾、開關雜訊、非單調性、電源雜訊。

所有與訊號完整性雜訊問題有關的問題可以總結為4類:

所有與訊號完整性雜訊問題有關的問題可以總結為4類:

- 單一網絡的訊號完整性

這裏面有一個很重要的概念,作為硬件工程師,一定要形成條件反射:

返回路徑

單一網絡的訊號質素與返回路徑物理特征有很大關系。如果記住這個點,很多layout的錯誤很容易被發現。

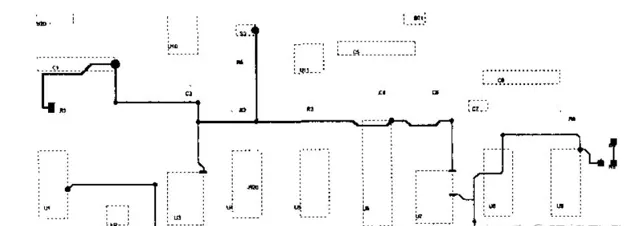

關鍵訊號要註意的點:

線寬是否變化(這個要更加特征阻抗確定)

參考平面是否完整

是否有分支線

特征阻抗是否連續

2. 兩個或多個網絡的串擾

這主要解決的是線與線之間的耦合關系,我們通常說3W間距,地孔隔離帶,減少平行走線的長度等就是為了解決線與線之間的幹擾。

這個地方可以從特征阻抗模型分析,平行線有電感耦合與電容的因素。這樣在訊號傳輸的過程中總有充放電和電磁耦合的現象。

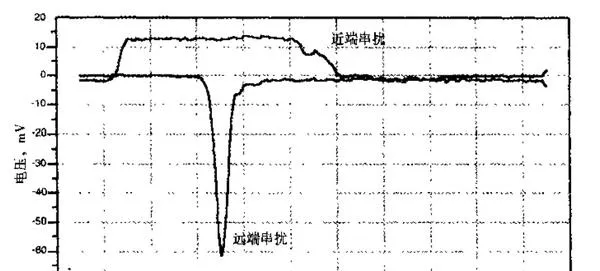

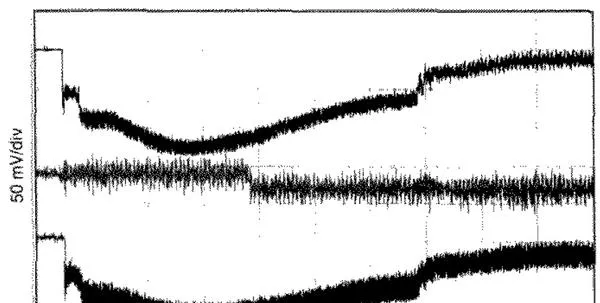

串擾可以分為近端耦合,與遠端耦合,近端耦合很容易飽和,遠端耦合幅值很大。

後面章節會具體說明。

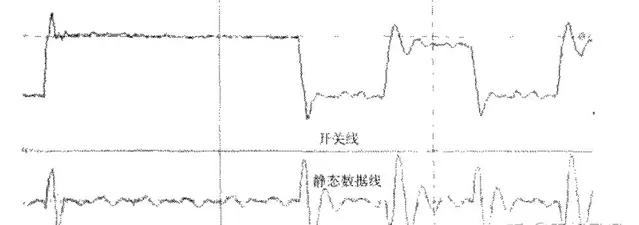

3. 電源和地的軌域塌陷

這個就是電源壓降。

本質上是由互連線之間的阻抗過大造成的。當電流過大,而目標阻抗過大所造成的電壓跌落現象。

也就是我們經常會看到,目標阻抗最小化問題。

在原理圖設計的時候:耦合電容的容值選擇,數量的選擇;

在PCB設計的時候:電容去耦半徑,過孔寄生電容和電感,電源層的設定,封裝寄生效應;

電源完整性我也會在後續章節來介紹。

4. 系統電磁幹擾和輻射

分為EMI和EMC

目前,國內開始重視EMC的管控,我的每個產品都有EMC要求,最近幾年基本上是解決EMC問題。因為這東西和原理關系不大,主要是參數選擇和布局走線的控制。

我們通常會聽到整改方案提到一對關鍵詞: 共模和差模 ;

共模輻射強度和頻率是線性關系。

差模輻射強度和頻率是平方關系。

輻射問題,我們要有意識的定位三個問題:

雜訊源 :這個過程就比較復雜了,需要你熟悉系統的訊號流向。

輻射路徑 :有線和無線

天線 :介面連線,插接

註:減小回路面積和伴地處理在很多情況下是非常有效的手段。

總結隨著專案經驗豐富,你會發現訊號完整信本質上就是在解決阻抗問題。

阻抗會引起訊號失真,會導致電源壓降,會導致輻射。

業界一直有兩種人:經驗主義和理論主義.

前者過分套用所謂的準則,讓設計很被動,總是畏手畏腳。

後者過分最求參數,雖然可靠性上來了,但是設計成本和周期也成倍增長。

我認為,結果是最好的經驗,一切都要在成本和時間面前妥協。

有限的精力放在相對關鍵的訊號上。

其他訊號,多一點少一點,關系真不大。

後面文章中,我會從多個角度重點分析。

關註王叔日記

你的點贊加關註將是激勵我持續輸出動力!