今天想談一下CXL,算是從GPU談異構(15)吧

寫東西比較隨意,想到啥,因為上周恰好看到了CXL 3.0的一些rumor和可能的feature,然後又恰好看了一下思科的NetDam論文,觸景生情,感慨頗深,不由得想扯兩句。

我曾經提過一個問題,問的是類似這些協定的CC有什麽用。

這個問題提的不太好,因為我發現即使不鉆進CC這個牛角尖上,從整個業界的芯片設計來看,CXL到底有什麽價值,可能都沒有公司特別是startup提出清晰的願景。

重新提一下問,也希望好事的同學們有能力的,在面對這兩年火熱的DPU公司、GPU公司。 「CXL這個技術,在你家XPU上到底能發揮什麽價值? 」

這是可以用作衡量一家公司能力的問題(ಡωಡ)

答案不言而喻, 價值巨大!

首先,CXL是intel對計算產業的一次巨大讓利這個利益,不是簡單地賣多少CPU返點那種。而是在處理器生態城墻上開啟了一個曾經絕對不會開啟的口子,一塊原本在intel嘴裏的蛋糕,它吐出來放到了桌子上。當然,能不能吃敢不敢吃,也是一種能力。

這個世界,一杯茶,那就是一個一個故事。

曾經講過幾個故事,沒有展開。實際上在過去幾十年的時間裏,CPU的儲存子系統部份,幾乎是被intel完整地封閉在它私有的生態裏面。

見過intel的合作合約的人可能不多,裏面嚴格限定了你能做什麽、不能做什麽,包括HP、dell、某想,任何想在記憶體上做點手腳的最佳化,都是不能做的。intel甚至一顆CPU,支持多大的記憶體,都能賣兩個價格。典型的某些記憶體數據庫,缺的不是算力,就是缺記憶體容量想擴充套件的,不行,你得買CPU才能擴記憶體。歷史上有很多個小公司嘗試過某些歪路子(例如利用QPI擴充套件的),要麽失敗,要麽被intel制止。連HP搞一個GEN-Z,也就是希望透過IO這個開口突破intel的封鎖。

那麽intel為什麽要讓出這塊蛋糕呢?

答案也不難,intel為了多賣CPU,連PCIe的演進速度都一直在進行壓制,就是不希望你有其他選擇,缺算力? 多買CPU啊。但是,皂滑弄人不是,牙膏太難擠了,而AI這一波的爆發,給了nvidia GPGPU的巨大增長空間。賣GPGPU越多,賣CPU就越少。

很好,你要是intel CPU的架構師,你該怎麽辦?

反正,這是第一次,intel願意放出一塊利益,他希望把在座的諸位GPU、DPU用作一把刀,來與nvidia形成某種制衡,雖然這塊蛋糕它隨時可以吃回去,但是在到那天之前(有沒有那天也是另說),你足以美滋滋地附著鯨魚吃一頓好的。

PS:CCIX在X86上(ARM另說)並不能像CXL那樣真正融入CPU MEMORY體系,只能做成PCIe的IO MEMORY。因為只有intel自己願意,才能真正把memory開放出來。

PS:題外的一個笑話,我是參加過CCIX協定制定的,為啥CCIX的介面 latancy比CXL差很多呢? 那是因為CCIX不敢修改被intel把控的PCIe的link layer(ARM還傻傻用這個做多P互聯,私有協定為啥link層相容PCIE?),而CXL是intel提出來的,說改,linklayer就改了唄……

然後,美味的食材需要一個優秀的廚子我一直都很好奇國內這些startup有沒有在CXL上給VC吹吹牛,因為這個食材上,是完全可以做出獨具風味的地方美食的。

intel在CXL 2.0 spec連結如下

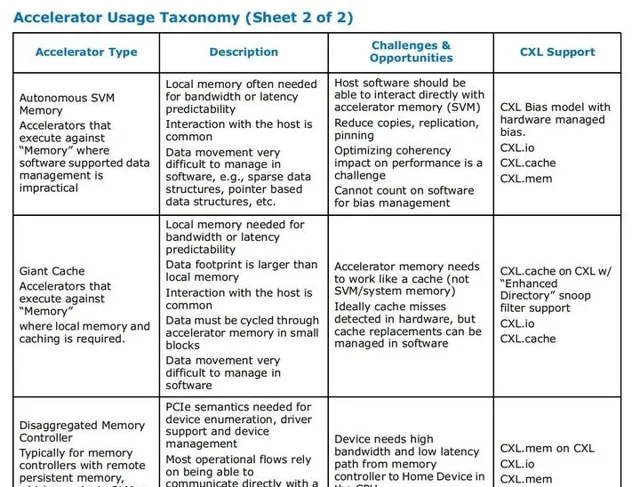

在其appendix A中,其實已經給出了菜譜的引導。但以我與各種同行、周邊交流的情況判斷,大多數人沒搞懂,更勿提這只是intel給的樣板菜,真實的變化更加豐富多彩

來舉一個典型不在菜譜中的CXL的好菜,就是思科的NetDAM,順著論文看了幾篇其作者zartbot的貼文,他在貼文中瘋狂打臉國內DPU,令人扼腕的是看不到一個敢於反抗或者澄清的……

╮(╯_╰)╭

他是一個相當優秀的廚子,NetDAM是一盤相當美味的大餐,而且他寫文章講得很直白,就是你們這些XX趕快來跟我學啊…………

我這裏就用它做一個例子。

NetDAM當前采用了思科的memif介面方案,這玩意兒大概率是類似virio之類的軟件方案,我沒興趣細看,但NetDAM的核心還是在NIC創新地增加了一塊額外的NIC DRAM擴充套件,要真正實作儲存級別的擴充套件,對軟件體現出remote memory的內容,而要達成這個目標,最終得靠CXL才能實作其完整體。

表面上,你看完論文可以說NetDAM不就是網卡加個獨立記憶體麽? 實際上啊

重劍無鋒,大巧不工!!

我從我的視角交叉佐證一下它存在的邏輯

- 伺服器CPU的記憶體是DIMM,為什麽有DIMM? 實際上是CPU需要的DRAM silicon size太大平攤放不下,所以采用了Z軸折疊的方式,用3D空間換容量來的。但是NIC這東西,需要的是獨立、小容量的DRAM,用寶貴的空間換來的DIMM來做NIC的DRAM,天然就是虧的。只要能獨立定義的DRAM訴求,最好就不要和DIMM合一。你喜歡喝雞湯,他喜歡吃牛肉,如果目標都清晰了,何必亂燉在一起?

- CPU的記憶體通道數量最多就是8通道了,這個不是不能做更多(也有12通道的CPU存在),而是當DDR通道超過8通道之後,無論是基板、PCB的代價就急轉而上,走入一種成本你幾乎無法承受的空間。如果按DDR5 5200速率算,8通道DDR頻寬是5.2*8*8=330GB。而一個400Gbps的NIC,其實按我經驗的演算法,外部頻寬折合到DDR頻寬是有一個1.5X放大倍數的,簡單來說要跑滿RX和TX雙向,需要400*2*1.5=150GB,NIC吃一半,CPU還玩個屁。這裏,如果放棄DIMM用貼片DRAM,在NIC card上滿足小容量150GB這個訴求是容易達成的。

- 很多人沒認真算一下400Gbps對DDR存取意味著什麽。光看TX,意味著每1ns要均勻獲得~512bit數據,如果按DDR存取延遲200ns及存取粒度64B,需要200 outstanding request,並且能均勻地應答響應。這是DDR難以做到的。

其實要解決400Gbps NIC問題,就只有兩條路:

- NIC與CPU進一步緊耦合,直接基於TB頻寬級別的cache互動數據。

- NIC與CPU進一步分離,各自有獨立的記憶體空間。

NetDAM選擇了第二條路,而這條路上,如果要讓作業系統或者說系統協定棧能夠直接操控NIC記憶體,最佳的搭配就是CXL。

PS:第一個開放DOCA_malloc庫的DPU公司也許將成為最終的獲勝者。

NetDAM是CXL能夠做出的一道相當不錯的好菜,如果舉目四望,廣闊天地還有更多的好菜可做。隨口舉個例子,誰說做CXL.cache就真的要在ACC上做一個CACHE? 你用cache機制來實作transactional memory它不香嗎?

廚子,刀在手,怎麽用,存乎一心。

最後,做好CXL很有可能短期在中國國內獲得獨特的效能優勢哦

最後,做好CXL很有可能短期在中國國內獲得獨特的效能優勢哦

如我曾經寫的關於創新的理解,有的公司會因為某些不可說的非技術原因,在技術創新上會有不可為的情況。

但留下的時間亦不多了。