自動駕駛汽車的確需要專門搭建相應的計算平台,這也是電腦系統硬件和軟件設計、開發的基礎。

硬件的基礎是CPU,軟件基礎是作業系統。當傳感器接受到資訊後,數據被匯入計算平台,由芯片進行運算處理。以上的過程對於安全性和即時性都有要求。

現階段被行業普遍套用的自動駕駛汽車計算平台有四種。

GPU計算平台

GPU的多核心、高記憶體頻寬,在並列運算、浮點運算上的效能是CPU的數十倍甚至上百倍。

憑借其計算能力以及對深度學習套用的支持,GPU現在是自動駕駛技術開發的主流平台了。

說到GPU計算平台,就得說下輝達。

其為自動巡航開發的NVIDIA DRIVE PX2平台是開放式的AI汽車計算平台,能夠讓車企和一級供應商迅速進行自動駕駛技術的研發和生產。

輝達還提供一套DriveWorks的用於自動駕駛軟件開發的套件(SDK),可以提供用於構建目標檢測,地圖定位、路徑規劃等計算密集型演算法的基礎。

借助上述的平台和套件,汽車ADAS系統可以清晰分辨出各大種類的汽車、摩托車、單車、行人。

而且整個NVIDIA DRIVE PX2硬件設施高度整合化,巴掌大小,消耗功率僅10W左右,使用深度神經網絡來處理多個網絡攝影機和傳感器的數據,並采用傳感器融合技術得到完整、準確的環境數據。

輝達開發此平台,盡可能讓汽車自身擁有人工智能和態勢感知平台,讓汽車能自行規避周圍的危險。

現在采用輝達平台方案的有寶馬,特斯拉,沃爾沃等眾多廠商。

FPGA計算平台

采用可編程邏輯單元陣列,是一種高效能、低功耗的可編程芯片。

透過燒錄FPGA配置檔來自訂芯片內部的電路連線,且燒錄是可擦寫,可以根據產品需求進行不同的功能配置。

Xilinx在1984年創造出FPGA以來,在通訊、醫療、安防上面都有著極為廣泛的套用。

對比CPU和GPU,FPGA的優勢在於硬件配置靈活、能耗低、效能高及可編程等,十分適合感知類的計算。

以最先搭載L3級別的2017款奧迪A8為例,ADAS的核心zFAS搭載了四個核心原件。

Mobileye的EyeQ3,負責交通訊號辨識,行人檢測,碰撞報警,光線探測和車道線辨識。

輝達的K1負責駕駛員狀態檢測,360度全景。

英特爾(Altera)的Cyclone V負責目標辨識融合,地圖融合,自動泊車,預剎車,激光雷達傳感器數據處理。

英飛淩的Aurix TC297T負責監測系統執行狀態。

其中的Cyclone V Soc,就是Altera 提供的FPGA方案,提高傳感器融合,高效完成對各類目標的檢測。

DSP計算平台

數碼訊號處理是將事物的運動變化轉變為一串數碼,並用計算的方法從中提取有用的資訊。

數碼訊號處理器(Digital Signal Processor),則是一種特別適合進行數碼訊號處理運算的微處理器。

在設計方案中,DSP的數據和地址總線分開,允許取出和執行指令完全重疊。在執行上一條指令的時候,同時可取出下一條指令進行譯碼,大幅提升了微處理器的執行速度。

強大的數據處理能力和高執行速度,使得它十分適合自動駕駛套用中的計算。

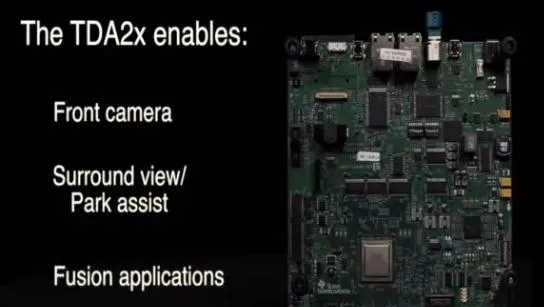

美國德州儀器公司(TI)是世界上最大的DSP廠商,也是DSP解決自動駕駛計算方案的宣導者。

他推出的TDA2X汽車系統級芯片,低功耗、高效能,能滿足高級駕駛員輔助系統(ADAS)設計要求。其系統級芯片(SoC)采用多相可升級的架構,包括固定和浮點 TMS320C66x數碼訊號處理器(DSP)產生核 ,Vision AcceleraTIonPac, ARMCortex-A15 MPCore™和雙Cortex-M4處理器.

TI的Vision AccelerationPac 還可補充TMS320C66x數碼訊號處理器(DSP)的內核,可以讓眾多的ADAS演算法同步執行。同時,TI TDA2X還可以作為融合雷達和攝像傳感器數據的中央處理器,幫助ADAS進行決策。

而另一家知名的DSP公司,美國的CEVA,2015年推出的CEVA-XM4,支持三維深度圖的生成和三維點雲的數據處理,單一CEVA-XM4的內核可以完成典型的「目標檢測與跟蹤」,功耗相當於現在先進CPU簇的10%,面積只有先進CPU簇的5%。

不過,CEVA可能更有名的就是它在通訊業務上的地位,2017年,有12億台通訊器材搭載了CEVA的DSP。(提供IP授權,不生產芯片)

目前為止,全球超過40%的手機使用CEVA的DSP內核,國內眾多手機,包括華為手機使用的也是CEVA授權生產的DSP(數碼訊號處理器)。

ASIC計算平台

專用集成電路,為特定需求專門客製的芯片。一旦設計制造完成,內部的電路和演算法就固定了,無法再改變。

體積小、功耗低、計算效能和計算效率高,因為芯片內部電路、演算法固定,容易量產,批次大所帶來的成本遞減效應明顯。

ASIC和FPGA的區別,類似房產推出的批次精裝修房和毛坯房裝修的區別。

精裝修房前期要規劃合適的裝修方案,確定各大供應商,試樣是否合格,中間可能要多次調整方案,在成本、效果、效率中衡量,需要一個較長周期,才能制作出合適的標準裝修樣版。前期裝修的花費高,確定樣版的周期長,但隨著量的鋪開,成本就會迅速下降。而毛坯房則是給客戶一個基礎,接好基本的水電氣,裝飾好外墻、裝好窗戶,後面的大量細節由客戶去確定如何裝修,相當於個人化的裝修,即便大量裝修毛坯房,由於每戶的毛坯房風格不同,裝修材料不同,裝修成本也很難降下來。

ASIC芯片研發費高,從研發到量產周期長(通常需要2-3年),前期開模投入高,但是效能優越,量產後成本會迅速下降。而FPGA研發速度快,一次性投入少,不需要介入芯片布局布線和工藝問題,可以隨時燒錄新的邏輯功能,但由於無法固定樣版,大量生產後,成本也降不下來。

但FPGA往往是ASIC客製的前哨站,往往FPGA確定某種燒錄效果好,需要大批次生產,就會轉為ASIC的模式。

業內現在比較知名的ASIC自動駕駛芯片的廠商有Mobileye(2017年被Inter收購).

Mobileye推出的視覺芯片EyeQ5,裝備有4種異構的全編程加速器,分別對電腦視覺、訊號處理和機器學習進行了演算法最佳化,可以達到L4級別自動駕駛的計算需求。

而最先搭載的EyeQ5的車型有可能是寶馬的純電動IX(國內還未上市)。

百度自動駕駛計算平台

百度 在2020年12月22日,宣布Apollo的自動駕駛計算平台ACU和德州儀器(TI)合作,搭載了TI的TDA4處理器,也就是DSP計算平台。

第一,多級處理,支持深度學習和即時影像處理;

第一,多級處理,支持深度學習和即時影像處理;

第二,功耗和效能效率表現突出,僅用5到20W的功耗和效能效率便可以

執行高效能ADAS操作,無需主動冷卻;

第三,有針對性的整合,帶有通用軟件平台的有針對性的整合SoC能夠降低系統復雜性和開發成本;

第四,能夠在單芯片上接入並處理4到6個三百萬像素網絡攝影機的數據,增強車輛感知能力和環視處理功能。

谷歌Waymo 的計算平台架構,2018年底還是采用的Altera的FPGA。

Altera的FPGA共有四大系列,分別是頂配的Stra ti x系列、成本與效能平衡的Arria系列、廉價的Cyclone系列、帶NVM的MAX系列。

但谷歌Waymo並沒有官宣最近的無人駕駛車輛所搭載的計算平台,業界評測可能混搭了FPGA/GPU/DSP。

2020年,Waymo第五代平台,搭載了29顆網絡攝影機,還有眾多的激光雷達和其他雷達,也許Waymo的計算平台真的需要探索目前算力的極限了。

參考:

自動駕駛技術系列叢書(清華大學出版社)