我們在前面功能安全架構系列專題文章 【功能安全的架構設計(一)】~【功能安全的架構設計(六)】

功能安全的架構設計(一) - 知乎 (zhihu.com)

功能安全的架構設計(二) - 知乎 (zhihu.com)

功能安全的架構設計(三) - 知乎 (zhihu.com)

功能安全的架構設計(四) - 知乎 (zhihu.com)

功能安全的架構設計(五) - 知乎 (zhihu.com)

功能安全的架構設計(六) - 知乎 (zhihu.com)

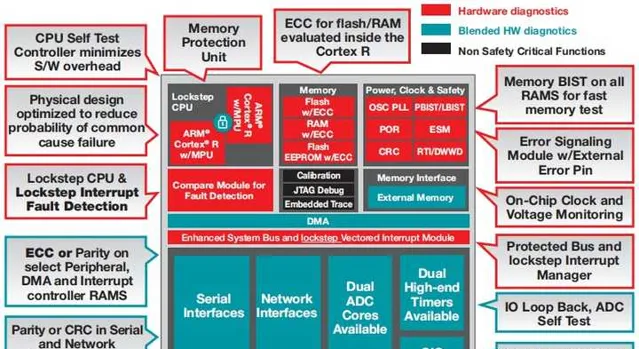

基本上把車載領域和工業領域的功能安全架構設計模型都介紹完了。本篇我們來談一談這些架構設計模型在處理器芯片中是如何體現的,看一看帶安全功能的處理器芯片在設計過程中都有哪些安全考量。如下圖TI Hercules微控制器架構呈現的安全特征,可以引發一些思考。

註:下文提到的芯片泛指控制器/處理器級的IIl類硬體器件。

不管是芯片的安全架構設計,還是下遊相關項系統的安全架構設計,在安全這塊無非都是要應對產品開發過程中的兩類失效,即隨機硬體失效和系統性失效。

接下來我們將從以下幾個方面來談一談處理器芯片的安全架構設計。

本期話題目錄:

1. 芯片硬體安全設計

1.1 雙核鎖步架構(DCLS)

1.2 芯片的供電安全

1.2.1 嵌入式電壓監控

1.3 芯片的時鐘安全

1.3.1 低功耗振蕩器時鐘檢測器(LPOCLKDET)

1.3.2 PLL差異檢測

1.3.3 雙時鐘比較器(DCC)

1.3.4 外部時鐘輸出監控(ECLK)

1.4 芯片的儲存安全

1.4.1 非儲存數位元件故障模型

1.4.2 記憶體故障模型

1.5 芯片溫度監控

1. 芯片硬體安全設計

微控制器(uC)的硬體安全設計一般透過 「安全島」(Safety/Security Island) 來實作。安全島是一個泛化的概念,類似於我們日常在十字路口等紅綠燈時所在的專門為行人建設行人等候區,也是一種「安全島」設施,它能為隔離人流和車流以及避免車輛失控撞向行人起到防護作用,芯片中的安全島也是專門設計的「獨立片區」用來實作安全相關功能,現在很多用於安全關鍵領域的芯片一般都會說明自己帶有安全島機制。

一般地,芯片上專門用於某個具有特定內容(如安全內容)的子系統或者內核,都可以用「Island」的概念來命名,主要強調局部設計的「獨立性」和「特殊性」。而用於配套實作芯片專有安全功能的專屬儲存單元、供電模組、外設、通訊匯流排等一系列IP的集合可以統稱為「安全島」。在「島上」可以相對獨立的執行安全相關的任務,安全島就是這樣一個給軟體提供安全任務執行的一個物理環境。

安全島模組一般獨立於芯片中的其他系統和內核,需要有單獨的電源域供電,單獨的計算單元,內部模組和記憶體需要有物理隔離機制,優先級較高的中斷機制,甚至是單獨的安全診斷單元,可以即時診斷出「島上」出現的問題,並且進入相應的安全狀態。

接下來我們從最小系統為出發點,談一談芯片安全島的實作方式。

1.1 雙核鎖步架構(DCLS)

雙核鎖步架構(DCLS)是一種片上冗余積體電路架構。在ISO26262並未針對片上冗余積體電路架構單獨提要求,但在IEC61508-2中對於帶片上冗余的積體電路特定架構提了相關要求。

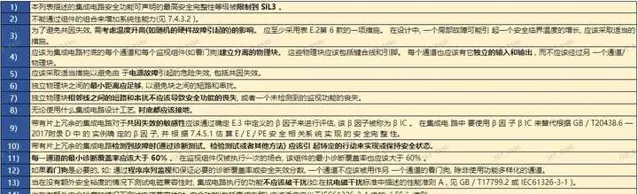

為了允許在 同 一個半導體襯底上 使用片上冗余, 以下給出了一系列要求。出於安全的原因該方法相對保守, 例如 , 它 被限制最高到SIL3 並且規定一系列限制性要求。以下要求僅與數位積體電路有關。可使用單半導體襯底來實作帶有硬體故障裕度大於零的子系統(片上冗余)。在這種情況下應履行所有以下要求 1) ~17), 並且E/E/PE 系統和積體電路的設計應滿足這些要求。(參考 IEC61508-2, Annex E)

參考上表的要求,我們來看下車載領域的功能安全微控制芯片在架構層面一般都會部署哪些安全措施,看是否能覆蓋上表的要求。

目前一些過了功能安全認證的微控制器芯片(如英飛淩的Aurix系列、NXP的MPC57XX/S32XX系列、TI的Hercules系列等)都采用了雙核鎖步架構設計,雙核鎖步作為處理器「安全島」概念的一部份,是一種1oo1D架構模型,既可以用於探測處理器硬體的故障也可以用於探測在CPU上執行指令的故障。

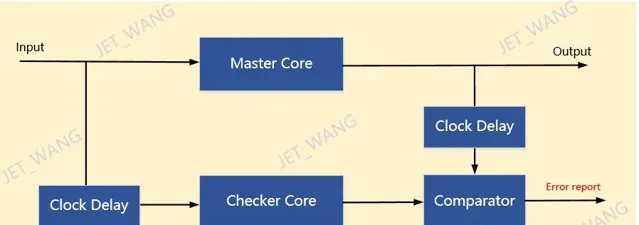

雙核鎖步架構的簡化示意可參考如下:

雙核鎖步架構的處理器一般具有如下特征:

> 目標:檢測微控制器中的硬體故障;

> 兩個核心都在同一個矽片(芯片)上實作,是一種片上冗余架構;

> 同一軟體在兩個核心上以同步模式執行;

> 在兩個核的輸出端配置有比較單元,在比較單元中對兩個核的輸出進行比較,如果檢測到差異,則發出錯誤訊號;

由於雙核鎖步架構屬於片上冗余系統,為了減少相關失效的的影響,一般需要采取了以下措施:

基於以上設計特征,我們常見的雙核鎖步參考架構如下。

1.2 芯片的供電安全

供電模組作為一個典型的相關失效引發源(DFI),芯片在設計過程中出於安全考慮需要為內核邏輯電路和 I/O 邏輯電路提供獨立的電源軌(包括模數轉換器 (ADC)、快閃記憶體泵和振蕩器),同時還會配備相應的電壓監控模組用於對各自電源軌功能異常的監控。

1.2.1 嵌入式電壓監控

安全芯片內部通常會設計嵌入式電壓監控器,此監控器能夠檢測超出範圍(OV/UV)的電源電壓。當電源遠遠高於或者低於額定電壓時,電壓監控器將從內部驅動上電復位引腳,使處理器保持在安全執行狀態。當電源處於範圍之內,電壓監控器將不會觸發處理器復位。

由於供電模組在芯片內部屬於通用基礎設施,具有共用性。一般芯片中所有功能模組都需要有供電才能執行,不同模組需要的工作電壓還不一樣,怎麽樣控制不同模組件用電串擾的影響就是芯片設計過程中的安全考量之一。通常,為了消除/減輕其引發共因失效的影響,芯片設計上通常給冗余內核和I/O邏輯電路的供電是獨立的。

提到相關失效,這裏我們先介紹下該術語涉及的基本概念。

> 相關失效 dependent failures: 不具有統計獨立性的失效,即失效組合發生的機率不等於所有考慮的獨立失效發生機率的乘積。

Jet Note: 簡單理解,相關失效是指兩個以上的獨立事件發生失效的原因存在一定相關性/關聯性,且導致該相關性的原因有多種。比如小王和老李在同一辦公室辦公,某一天小王出現了咳嗽、流鼻涕的感冒癥狀,隔天老李也出現了感冒癥狀,小王和老李都出現了感冒癥狀這事就存在一定的相關性。

由於導致失效存在相關性/關聯性的方式不同,相關失效包括共因失效和級聯失效。

> 共因失效(Common Cause Failures-CCF): 由於共同原因,兩個或多個部件故障狀態同時存在,或在短時間間隔記憶體在的相關失效子集。

共因失效是指冗余元件的獨立通道上兩個或多個元件的隨機故障狀態重合,導致定義的元件無法執行其預期安全功能,這是由單一事件或根本原因(偶然原因、不可分配原因、雜訊、自然模式等)引起的。

Jet Note: 同樣拿上面小王和老李的故事來舉例。小王和老李在同一辦公室辦公,小王感冒後沒多久老弟也出現了感冒癥狀,小王和老李都出現了感冒癥狀這事都要歸因於流感病毒,所以是流感病毒導致小王和老李發生的」共因失效「。

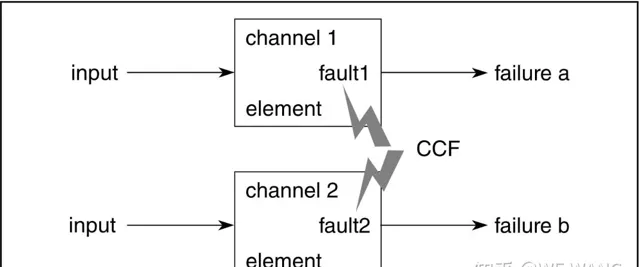

> 共模失效(Common Mode Failure-CMF): 共因失效的一個子集。冗余通道中兩個或多個(不一定相同)元件中隨機故障的重合導致安全功能方面相同的重合錯誤行為。由於故障相同,比較器不會檢測到故障。下圖顯示了兩個不同但冗余的通道內的兩個元件,其中一個根本原因導致兩個不同的故障(fault1、fault2),從而導致兩個元件和兩個通道中的相同失效(failure a)。由於兩個通道中都發生了相同的失效,功能安全比較器機制無法檢測到失效。

Jet Note: 共模失效是一種特殊的共因失效,簡單理解它是一種從結果上看以相同模式失效的共因失效。繼續拿上面小王和老李的故事來舉例。小王和老李在同一辦公室辦公,小王和老李都出現了感冒癥狀,受流感病毒的影響兩人都出現了發燒、咳嗽及鼻塞流鼻涕的癥狀導致兩人無法集中註意力辦公於是中斷當前工作都請假去了醫院,這種情況下流感病毒導致小王和老李發生了」共模失效「。

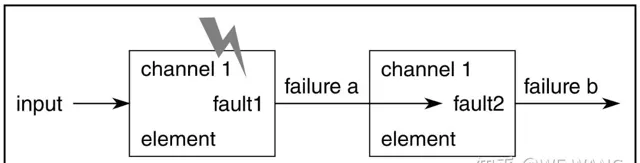

> 級聯失效(Cascading Failures-CF): 當系統中某個元件的局部故障波及互連元件,導致同一系統和同一通道內的另一個或多個元件發生故障時,就會發生級聯失效。級聯失效是非共因失效的相關失效。下圖顯示了一個通道內的兩個元件,單一的根本原因導致一個元件中的故障(fault 1),從而導致某個失效(failure a)。然後,該失效級聯到第二個元件,導致第二個故障(fault 2),進而導致另一個失效(failure b)。

Jet Note: 級聯失效強調的是在同一系統/同一通道內的失效級聯。接著上面小王和老李的故事來舉例。小王和老李在同一辦公室辦公,老李出現了感冒癥狀,但小王未受到影響。受流感病毒的影響老李先是喉嚨幹癢導致咳嗽,接著出現嚴重鼻塞導致嗅覺失靈,還伴隨間歇性的耳鳴導致聽力下降,隨著咳嗽不停病情加劇出現了呼吸道感染導致咽喉腫痛聲帶受損無法正常發聲。這種情況下流感病毒導致老李身體中的耳、鼻、喉各功能模組發生了」級聯失效「。

介紹完相關失效的相關概念,我們來看下芯片設計過程中對於供電模組可能導致的相關失效一般會采取什麽措施。

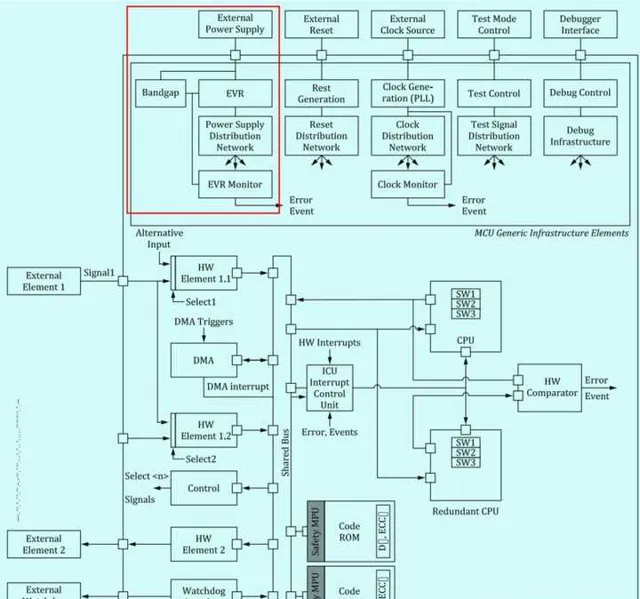

如下有一處理器芯片的部份內部元件示意圖,紅框部份是芯片內部電壓調節元件。

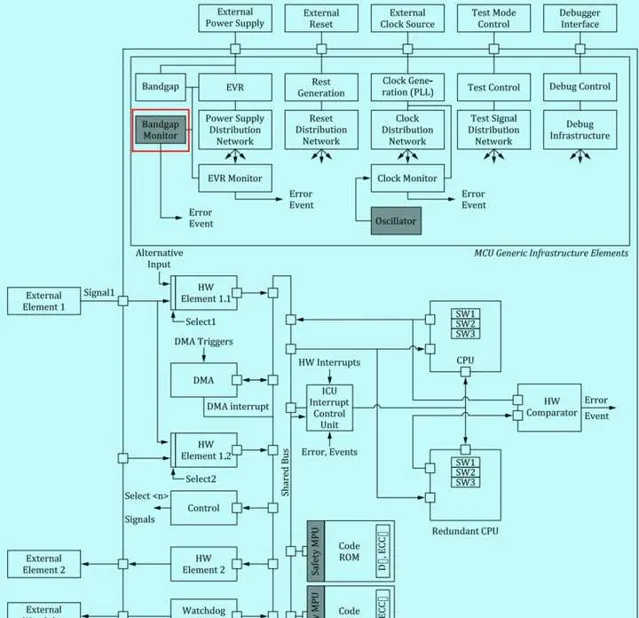

圖中的EVR(Embedded Voltage Regulator)被辨識為芯片內部的共享資源,由該調節器透過內部其他供電網路給芯片內部其他元件供電,示意圖中還顯示了該芯片內部有一個電壓監控模組(EVR Monitor)用於對EVR的電壓進行監控。

EVR(嵌入式穩壓器): 除由「外部供電電源」供電的輸入/輸出焊盤外,EVR可以為處理器芯片內的每個硬體要素提供電源。

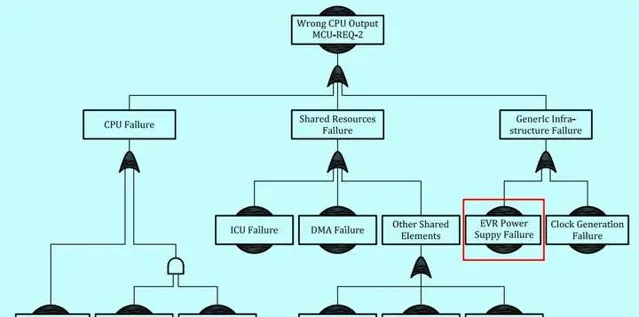

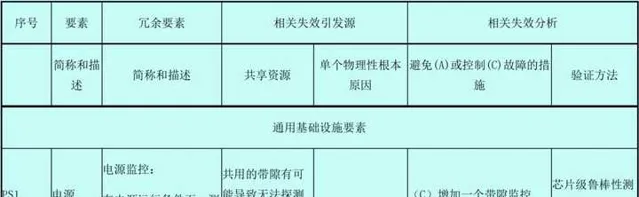

假設該芯片按照功能安全標準要求開發過程中有如下要求分配給了處理器。

MCU-REQ-2: 導致 CPU 輸出錯誤的隨機硬體故障,應在 20 毫秒內被檢測到[ASIL X]。

-MCU-REQ-2.1: 「中央處理單元CPU應由冗余CPU監控。CPU和冗余CPU的輸出透過硬體比較器在每個時鐘周期都進行比較」;及

-MCU-REQ-2.2 :「當CPU和冗余CPU的輸出出現不匹配時,應生成錯誤事件」。

基於上方處理器內部元件模組對該安全要求 [MCU-REQ-2] 實施故障樹分析如下。

根據上方的故障樹分析辨識出的共享資源和冗余要素,得到該處理器中關於供電模組的相關失效分析如下。

根據上方DFA分析結果,在原來芯片架構的基礎上 增加新的帶隙監控元件 ,使與帶隙漂移失效模式相關的相關失效被減輕。針對供電模組考慮了安全因素之後在架構上增加了相關安全模組,範例處理器芯片的內部架構更新如下。

以上範例只是為了說明芯片設計過程中對於安全內容的考量是如何實施的,從範例可以看出針對功能安全的芯片架構設計在哪些地方需要增加什麽電路也是要經過一番安全分析來得到,從設計到實施再到驗證也都需要遵照標準的流程來確保完整性、一致性和可追溯性。

1.3 芯片的時鐘安全

芯片內部的時鐘管理邏輯電路一般包括時鐘源、時鐘生成邏輯電路,此邏輯電路包括鎖相環路 (PLL) 的時鐘倍乘、時鐘分配器、和時鐘分配邏輯電路。

針對時鐘管理電路的組成模組,以某一安全微控制器為例,芯片設計過程中一般會考慮以下檢測電路用來應對時鐘管理電路的各種可能的失效模式。

1.3.1 低功耗振蕩器時鐘檢測器(LPOCLKDET)

低功耗振蕩器時鐘檢測器 (LPOCLKDET) 是一個可被用於檢測主時鐘振蕩器故障的安全診斷。

LPOCLKDET 采用嵌入式高頻、低功耗振蕩器 (HF LPO)。時鐘檢測電路工作方式為檢驗一個其它時鐘上升沿之間的某一個時鐘(振蕩器或者 HF LPO)上的上升沿。結果就是除了標記不正確、頻率重復,電路也會由於瞬態情況發生故障。

1.3.2 PLL差異檢測

PLL 邏輯電路包括一個能夠檢測一個 PLL 輸出時鐘差異的嵌入式診斷。差異是由基準時鐘和反饋時鐘間的相位釘選損失造成。錯誤響應和指示取決於系統模組內的 PLL 控制寄存器的設計。

1.3.3 雙時鐘比較器(DCC)

一個或者多個雙時鐘比較器 (Dual Clock Comparator-DCC) 被使用為多用途安全診斷。DCC 可被用於檢測不正確頻率和時鐘源之間的漂移。DCC 由兩個計數器塊組成:一個計數器塊被用作一個基準時鐘而另外一個被用作測試時鐘。基準時鐘和處於測試中的時鐘均可由軟體進行選擇,可作為時脈的預計比率。與預計比率的偏差會生成一個錯誤訊號。

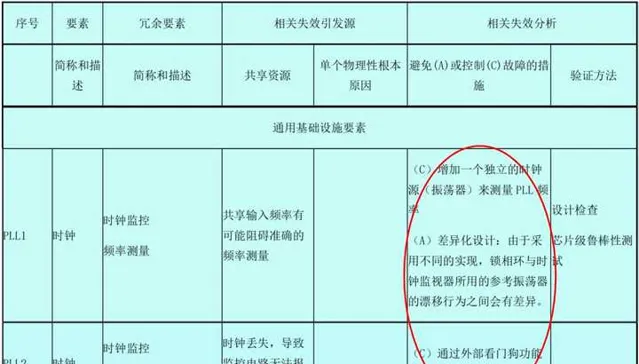

處理器時鐘電路也是一個典型的通用基礎設施模組,其隨機硬體失效導致的相關失效也是需要在芯片設計過程中給予考慮。

繼續以上方處理器內部元件範例為例,先透過實施FTA辨識出相關失效引發源(DFIs),然後基於辨識的DFIs開展相關失效分析。

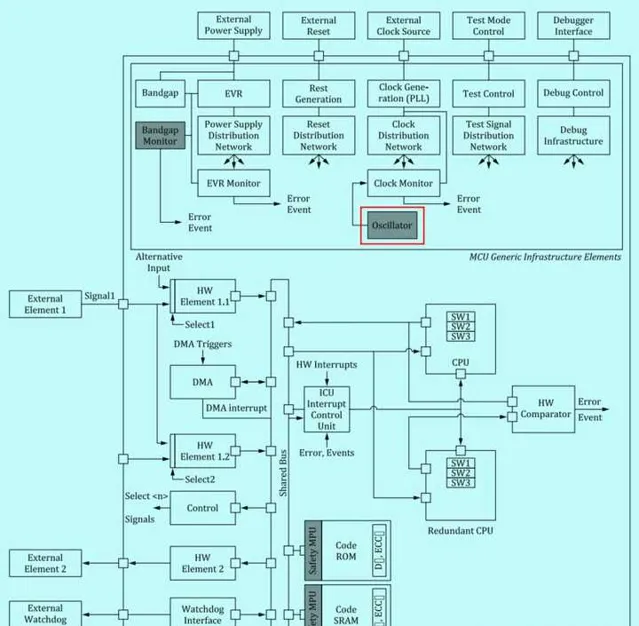

根據上方的故障樹分析辨識出的時鐘作為相關失效引發源,得到該處理器中關於時鐘電路的相關失效分析如下。

根據上方DFA分析結果,在原來芯片架構的基礎上增加新的振蕩器元件,使與時鐘漂移失效模式相關的相關失效被減輕。針對時鐘模組考慮了安全因素之後在架構上增加了相關安全模組,範例處理器芯片的內部架構更新如下。

1.4 芯片的儲存安全

數據在尋址、寫、儲存和讀過程中的會經過芯片的數位電路元件和記憶體,以下將從這兩方面來談一談芯片設計過程中對於數據的儲存有哪些安全考量。

1.4.1 非儲存數位元件故障模型

芯片中的數位元件包括微控制器(uC)、片上系統(SoC)器件和專用積體電路(ASIC)等元件的數位電路部份,也包括現場可編程門陣列(FPGA)。

通常,芯片的非儲存數位元件通常包括以下故障模型:(參考ISO 26262-11:2018, 5.1.2)

】永久性故障(permanent fault) ,也稱為 「硬錯誤/硬故障」 ,該故障類別的具體故障模型詳細描述如下。

• 卡滯故障(stuck-at fault): 電路中的故障特征為不管輸入激勵如何變化,節點保持在邏輯高(1)或邏輯低(0)的狀態;

• 開路故障(open-circuit fault): 透過將一個節點破壞為兩個或多個節點,從而改變節點數量的電路故障;

• 橋接故障(bridging fault): 意外連線的兩個訊號。根據所采用的邏輯電路,可能導致「線或」或者「線與」的邏輯功能。通常僅限於設計中物理上相鄰的訊號;及

• 單粒子硬錯誤(Single Event Hard Error-SHE): 由單次放射線事件導致執行的不可逆變化,通常與器件中一個或多個要素的永久性損壞(如柵極氧化物破裂)有關。

】瞬態故障(transient fault) ,也稱為 「軟錯誤/軟故障」 ,該故障類別的具體故障模型詳細描述如下。

• 單粒子瞬態脈沖(Single Event Transient-SET): 由於單個高能粒子穿過,造成積體電路某節點瞬時電壓漂移(例如,電壓尖峰);

• 單粒子翻轉(Single Event Upset-SEU): 由高能粒子穿過引發的訊號所造成的軟錯誤;

• 單位元位翻轉(Single Bit Upset-SBU): 單粒子造成的單個儲存單元翻轉;

• 多單元翻轉(Multiple Cell Upset-MCU): 單粒子引起積體電路中的多個位元位同時失效。錯誤位通常(但不總是)在物理上相鄰;及

• 多位元位翻轉(Multiple Bit Upset-MBU): 兩個或多個由單粒子引起的同一個半字節、字節或字中的位元位錯誤。多位元位翻轉不能透過簡單的錯誤更正碼(ECC)進行校正(例如,單位元位錯誤校正)。

Jet Note: 單粒子瞬態脈沖(SET)、單粒子翻轉(SEU)、單位元位翻轉(SBU)、多單元翻轉(MCU)和多位元位翻轉(MBU)通常表示為「軟錯誤」,之所以被稱為軟錯誤, 是因為電路本身並未受到放射線的永久損壞。

1.4.2 記憶體故障模型

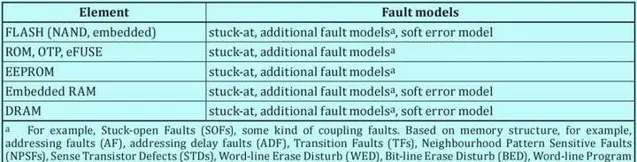

記憶體故障模型可能因儲存架構和儲存技術而有所差異。半導體記憶體的典型故障模型如下表所示。

該表並不完備,也可以根據其他已知故障或結合實際套用進行調整。

芯片內部或外部的儲存模組都對高能粒子比較敏感,由上圖可知Flash和RAM具有軟錯誤故障模型,這是由其儲存架構和技術所決定。

當放射線事件引起足夠的電荷幹擾扭轉或翻轉低能量的半導體儲存單元、 寄存器、 鎖存器或觸發器的數據狀態時, 軟錯誤就會發生。

軟錯誤可能和各類可變記憶體相關, 比如動態內 存( DRAM )、靜態內 存( SRAM )、 微控制器中的寄存器組、 緩存( cache )、流水線( pipelines )、裝置(如 ADC 、 DMA 、 MMU )配置寄存器、中斷控制器、復雜定時器等。對alpha粒子和中子(Neutron)的敏感度由核心電壓和物理結構決定。

標準給出了關於記憶體故障的安全機制/措施的描述及其可實作的典型診斷覆蓋率,參考如下。

ECC在現在的安全微控制器芯片中都會部署相關電路用於檢測並糾正記憶體中的位錯誤。

記憶體保護單元(MPU)也是現在的安全微控制器芯片中部署的專門用於實施記憶體分區、隔離的安全電路模組,防止不同數據儲存區域未授權的存取。

由於軟錯誤是在記憶體身上非常具有代表性的故障,其他關於芯片設計過程中考慮的記憶體包括軟錯誤在內的故障防護的技術我們將在單獨的文章中進行介紹。

1.5 芯片溫度監控

最小系統中時鐘、電源、記憶體都是典型的共因失效引發源,除了這些芯片內部元件故障引發的相關失效需要在設計過程中給予考慮外,對於電氣串擾和環境應力可能引發的相關失效在芯片設計過程中也需要加以考慮。

芯片內的或外部對芯片的電氣串擾在芯片設計過程中會同步進行考慮,如采用低抖動的時鐘源,減小時鐘網路的幹擾。在芯片內部采用金屬遮蔽層或導電襯底來隔離敏感區域或雜訊源,從而減小電磁幹擾的影響等。

另外對於數據存取的免於幹擾芯片設計過程中會考慮空間和時間上的隔離措施,比如上面提到的MPU就是使用了記憶體空間物理隔離或基於時間的存取隔離技術。

這裏我們要談一談芯片設計過程中對於溫度的考慮。

像動物一樣在一個舒適的溫度環境下動物生長的最快生態體征也最好,套用半導體技術的芯片在合適的溫度下其功能和效能也表現為最佳。通常,高溫會導致芯片發生不可逆的損壞,而低溫導致的芯片功能異常往往是可恢復的。異常的溫度(通常是高溫)不僅會導致芯片工作異常,還會加速芯片的老化影響芯片的壽命,同時加大了系統功耗,使整個系統的可靠性降低。

所以芯片設計過程中往往會對溫度的影響給予考慮。對於功能安全來說,溫度這種環境應力是典型的相關失效引發源,所以實施安全設計的芯片基本都會在內部部署溫度傳感器來監控芯片的內部溫度。典型地,雙核鎖步架構的微控制器中一般每個核都會部署一個專有的溫度傳感器用於監控核溫,當檢測到溫度超出預設的範圍值(如,-40℃~150℃)時輸出一個溫度狀態訊號,芯片自身進入fail-safe狀態並輸出一個故障訊號給到上層系統。

在芯片內部部署溫度傳感器對核溫進行監控屬於探測措施,實際芯片設計過程中除了探測類的安全措施外,預防措施也會同步進行考慮,比如芯片的散熱設計。

芯片內部的散熱設計不僅可以降低功耗提升芯片效能,也有助於保證芯片的安全完整性要求。下方舉了些常見的芯片散熱技術,供參考。

> 增加散熱層: 在芯片封裝中增加散熱層,將芯片產生的熱量傳遞到封裝表面,再透過散熱器將熱量散發出去。散熱層可以采用金屬、陶瓷等導熱材料。

> 熱管技術: 熱管是一種高效的傳熱元件,可以在較小的空間內傳遞大量的熱量。在芯片內部,可以將熱管與芯片的散熱區域連線,將熱量快速傳遞到熱管的另一端,再透過散熱器散發出去。

> 熱設計最佳化: 透過最佳化芯片的熱設計,減少熱阻和散熱路徑,提高散熱效率。例如,合理布局芯片內部的發熱元件、最佳化芯片的散熱通道、加強封裝材料的導熱效能等。

功能安全的微控制器架構內部還有很多其他硬體的安全措施,想要了解更多各位可以結合芯片安全手冊去學習,然後對映到標準的相關要求中去,這可能是最便捷的芯片功能安全設計的方式。

以上關於芯片的硬體安全設計就介紹到這裏,限於篇幅,接下來的芯片軟體安全和資訊保安設計將在下一篇文章中和大家談一談。

參考:

[1] ISO 26262-5:2018 Product development at the hardware level

[2] ISO 26262-9:2018, Automotive safety integrity level (ASIL)-oriented and safety-oriented analyses

[3] ISO 26262-11:2018 Guidelines on application of ISO 26262 to semiconductors

[4] IEC61508-2:2010 Requirements for electrical/electronic/programmable electronic safety-related systems

[5] IEC61508-7:2010 Overview of techniques and measures

[6] MPC5746RRMAD Rev. 3, 06/2017

[7] 針對TMS570LS04x 和 03x的安全手冊 Hercules™ARM® 安全微控制器的安全手冊使用者指南

關於FTA系列專題文章(共6篇)已全部就緒,請進入下方連結或掃碼選擇查閱。

http:// t.a0f.top/56Q4D/upNZP17 8

關於FMEA七步法的專題文章全集已就緒,請進入下方連結或掃碼查閱。

http://t.a1b.top/56Q4D/RM1mkMP

連結 (FMEA七步法)

連結 (FMEA-MSR)

連結(FMEA之特殊特性)

為收集大家的寶貴意見以及方便大家進行交流,集思廣益,已建立公眾號同名交流群,有需要入群的讀者請添加下方微信(WF_WANG-ANLUOVITA)以便邀請入群。

更多精彩內容歡迎關註:功能安全落地漫談